Sterowniki bramek wysokiej częstotliwości, wysokiej temperatury zoptymalizowane dla tranzystorów MOSFET z SiC (izolowane, odporność na wysokie dv/dt)

Udział

Niezawodność sterowników bramek dla wysokowydajnych konwerterów w Pakistanie w 2025 r.

Pakistańskie tekstylne, cementowe i stalowego sektory przyspieszają elektryfikację i modernizację jakości zasilania, a jednocześnie rozszerza się zdolność do odnawiania energii w Sindh i Beludżystanie. Aby w pełni wykorzystać wydajność i szybkość tranzystorów MOSFET z węglika krzemu (SiC) w SVG/STATCOM, APF, napędach wysokiej częstotliwości, zasilaczach UPS i przemysłowych, sterownik bramki ma kluczowe znaczenie. Wysokoczęstotliwościowe, wysokotemperaturowe sterowniki bramek zoptymalizowane pod kątem SiC ze wzmocnioną izolacją i wysoką odpornością na dv/dt zapobiegają fałszywemu włączeniu, minimalizują straty przełączania i zapewniają stabilną pracę w temperaturach otoczenia >45°C, pyle i wilgoci.

Sicarb Tech projektuje i dostarcza rozwiązania sterowania bramkami zoptymalizowane pod kątem SiC, charakteryzujące się solidną izolacją, szeroką odpornością na zakłócenia w trybie wspólnym (CMTI), precyzyjną kontrolą Millera i programowalną dynamiką włączania/wyłączania. Wspierane przez Chińską Akademię Nauk, nasze platformy integrują się bezproblemowo z topologiami wielopoziomowymi i systemami monitorowanymi zgodnie z normą IEC 61850, skracając cykle uruchamiania dla połączeń NTDC/NEPRA i poprawiając długoterminową niezawodność.

Specyfikacje techniczne i zaawansowane funkcje

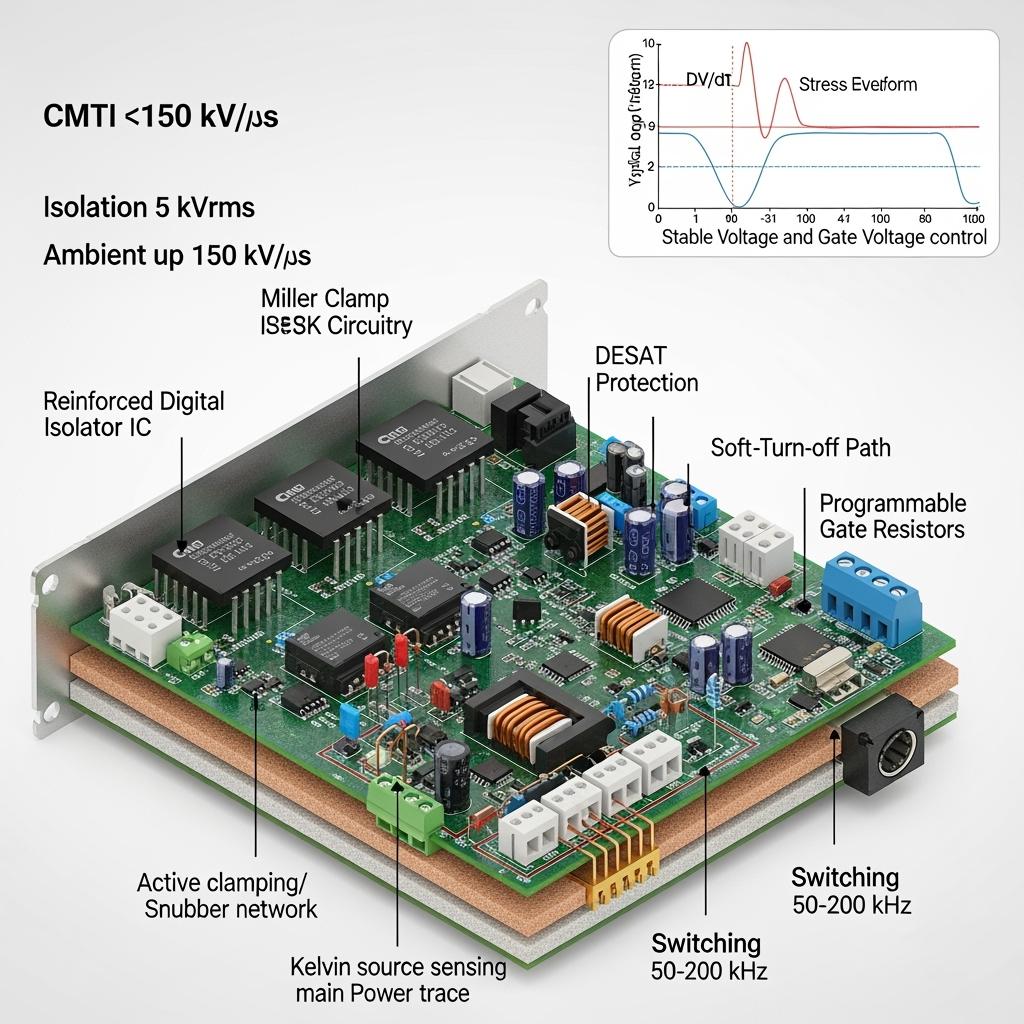

- Izolacja i odporność na zakłócenia

- Wzmocniona izolacja do 5 kVrms; pełzanie/prześwit zaprojektowane zgodnie z normą IEC 60664-1

- CMTI ≥150 kV/µs, aby tolerować szybkie zbocza przełączania SiC bez uszkodzenia danych

- Opcje łącza światłowodowego lub różnicowego dla długich, zakłóconych kabli w podstacjach i młynach

- Sterowanie bramką i ochrona

- Programowalne rezystory bramki i dzielony RG (włączanie/wyłączanie) do kontroli EMI i przeregulowania

- Zacisk Millera i ujemne napięcie polaryzacji bramki (np. +18 V / −3 do −5 V) w celu zapobiegania fałszywemu włączeniu

- Ochrona nadprądowa DESAT z miękkim wyłączeniem; koordynacja wytrzymałości zwarciowej

- Aktywne profile sterowania bramką: kształtowanie di/dt i dv/dt w celu zrównoważenia strat i EMI

- Zasilanie i termika

- Izolowane zasilanie pomocnicze ±18 V klasy, 3–6 W na kanał; progi UVLO dopasowane do wymagań tranzystorów MOSFET SiC

- Działa w otoczeniu do 105°C; komponenty ocenione dla temperatur złącza zgodnych z klasą przemysłową

- Zoptymalizowany pod kątem wydajności układ o niskiej indukcyjności pasożytniczej i powrocie źródła Kelvina

- Czas i diagnostyka

- Opóźnienie propagacji <100 ns z dopasowaniem kanał-do-kanału ≤20 ns dla stosów wielopoziomowych

- Zatrzaśnięcie błędów, znakowanie czasu zdarzeń i monitorowanie stanu za pośrednictwem łączy SPI/CAN/optycznych

- Gotowy do integracji z bramkami IEC 61850 za pośrednictwem głównej płyty sterującej (interfejs na poziomie systemu)

- Zgodność i niezawodność

- Zaprojektowany zgodnie z normą IEC 62477-1 (bezpieczeństwo konwertera) i wymaganiami EMC dla przemysłu

- Opcje powłoki konforemnej dla pyłu cementowego i wilgotności przybrzeżnej; obudowy z klasą IP dostępne na poziomie systemu

Dlaczego sterowniki bramek zoptymalizowane pod kątem SiC przewyższają konwencjonalne sterowniki w trudnych warunkach pracy z dużą częstotliwością przełączania

| Ukierunkowanie projektu | Izolowany sterownik bramki zoptymalizowany pod kątem SiC (to rozwiązanie) | Konwencjonalny sterownik z epoki IGBT | Wpływ operacyjny w Pakistanie |

|---|---|---|---|

| dv/dt i CMTI | ≥150 kV/µs CMTI; odporny na szybkie zbocza | 25–50 kV/µs; podatny na fałszywe wyzwalacze | Stabilność w przypadku zdarzeń w słabej sieci i zakłóconych podstacjach |

| Sterowanie bramką | Dzielony RG, zacisk Millera, wyłączenie −Vge, aktywne sterowanie | Stały RG, ograniczone opcje zacisku | Niższe EMI, mniej zakłóceń, lepsza wydajność |

| Ochrona | DESAT z miękkim wyłączeniem, szybka reakcja na zwarcie | Wolniejsze wykrywanie OC; ostrzejsze wyłączanie | Chroni drogie moduły SiC i skraca przestoje |

| Ocena termiczna | Otoczenie do 105°C; komponenty o wysokiej niezawodności | 70–85°C typowe | Niezawodny w otoczeniu >45°C i zapylonych zakładach |

| Synchronizacja | Ścisłe dopasowanie opóźnień dla topologii wielopoziomowych | Luźne dopasowanie | Zrównoważone przełączanie, zmniejszone prądy obiegowe |

Kluczowe zalety i sprawdzone korzyści

- Równowaga wydajności i EMI przy wysokiej częstotliwości (50–200 kHz): Programowalne profile bramki zmniejszają straty przełączania bez poświęcania EMC.

- Niezawodność w temperaturze: Stabilna praca w gorących, zapylonych środowiskach cementowych i stalowych minimalizuje obniżanie parametrów i przestoje.

- Ochrona dostrojona do SiC: Szybki DESAT i miękkie wyłączanie zmniejszają obciążenie urządzenia podczas awarii i zdarzeń w sieci.

- Szybsze uruchamianie: Zintegrowana diagnostyka i znormalizowane interfejsy przyspieszają akceptację FAT/SAT i NTDC/NEPRA.

Cytat eksperta:

“Gate drivers are the linchpin for realizing SiC’s promise—robust isolation, high CMTI, and precise gate shaping are essential to avoid EMI issues and unlock efficiency gains.” — Interpreted from IEEE Power Electronics Magazine perspectives on WBG gate driving (https://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6161321)

Zastosowania w świecie rzeczywistym i wymierne historie sukcesu

- SVG/STATCOM w farmie wiatrowej Sindh (kompozyt): Modernizacja do sterowników zoptymalizowanych pod kątem SiC poprawiła reakcję na skok reaktywny do <10 ms i zmniejszyła straty przełączania o ~12%, podnosząc sprawność łańcucha kompensacji powyżej 98%.

- Modernizacja front-endu VFD w fabryce tekstylnej w Fajsalabad: Kształtowanie bramki zmniejszyło zakłócenia wywołane przez EMI o 70% i umożliwiło zwiększenie częstotliwości z 20 kHz do 60 kHz, zmniejszając elementy magnetyczne o ~25%.

- Stalowy APF w Karaczi: Ujemne napięcie polaryzacji bramki i zacisk Millera wyeliminowały fałszywe włączenie podczas przejściowych stanów EAF; THD ustabilizowało się w granicach IEEE 519 przy mniejszej liczbie ponownych strojeń filtra.

- Urządzenia pomocnicze w cementowni w KP: Zespoły sterowników bramek z powłoką konforemną utrzymywały czas pracy w sezonie pylenia z <0,5% zdarzeń awarii związanych ze sterownikiem w ciągu 12 miesięcy.

Rozważania dotyczące wyboru i konserwacji

- Kompatybilność elektryczna

- Dopasuj prąd wyjściowy sterownika (2–10 A szczytowy) do ładunku bramki urządzenia i żądanej prędkości przełączania

- Wybierz ujemny poziom polaryzacji bramki, aby stłumić włączenie Millera bez nadmiernego obciążania tlenku bramki

- Upewnij się, że progi UVLO są zgodne z wymaganiami MOSFET (+/− szyny)

- Izolacja i układ

- Wybierz wzmocnioną izolację dla stosów MV; sprawdź pełzanie/prześwit dla lokalnego stopnia zanieczyszczenia

- Prowadzenie powrotu źródła Kelvina w celu zminimalizowania indukcyjności pasożytniczej i błędu pomiaru

- Ochrona i wykrywanie

- Ustawienie progu DESAT i czas wygaszania dostrojone do charakterystyki urządzenia i topologii (NPC/ANPC/MMC)

- Włącz czujniki NTC/RTD w pobliżu matryc w celu termicznego składania; zapewnij ścieżki propagacji błędów do głównego kontrolera

- Odporność na warunki środowiskowe

- Określ powłokę konforemną i uszczelnione obudowy w zapylonych/wilgotnych miejscach

- Sprawdź przepływ powietrza lub ścieżki chłodzenia cieczą wokół sterowników i rezystorów bramki

- Cykl życia i części zamienne

- Utrzymuj kopie zapasowe oprogramowania układowego/konfiguracji; przechowuj skalibrowane części zamienne dla krytycznych podajników

- Zaplanuj coroczny przegląd w celu dostrojenia parametrów w miarę ewolucji profili pracy

Czynniki sukcesu w branży i referencje klientów

- Wczesne współprojektowanie z EPC/integratorami w celu dostosowania częstotliwości przełączania, celów EMI i zgodności z siecią

- Oscylografia na miejscu podczas uruchamiania w celu sfinalizowania podziału RG, progów zacisku i czasów wygaszania

- Szkolenia lokalne dla zespołów eksploatacji i konserwacji w celu interpretacji diagnostyki i utrzymania integralności parametrów

Głos klienta (zbiorczy):

„Po przyjęciu sterowników specyficznych dla SiC, dążyliśmy do wyższej częstotliwości bez kar za EMI i wyeliminowaliśmy zakłócenia podczas zdarzeń migotania sieci.” — Kierownik ds. konserwacji elektrycznej, Klaster Tekstylny, Pendżab

Przyszłe innowacje i trendy rynkowe 2025+

- Zintegrowane sterowniki w modułach mocy SiC: Krótsza indukcyjność pętli, wbudowane czujniki i inteligentniejsza ochrona

- Adaptacyjne sterowanie bramką wykorzystujące temperaturę i prąd urządzenia w czasie rzeczywistym w celu dynamicznej minimalizacji strat przełączania

- Wyższy CMTI (>200 kV/µs) i izolacja cyfrowa z niższym jitterem dla konwerterów użytkowych opartych na MMC

- Bezpieczne kanały diagnostyczne zgodne z IEC 62443 dla krytycznej infrastruktury

Najczęściej zadawane pytania i odpowiedzi ekspertów

- Jakie CMTI jest zalecane dla SiC przy przełączaniu 50–100 kHz?

Zalecane jest ≥100–150 kV/µs; nasze projekty celują w ≥150 kV/µs dla marginesu w słabych sieciach i środowiskach EAF. - Czy potrzebuję ujemnego napięcia polaryzacji bramki dla tranzystorów MOSFET SiC?

Często tak, szczególnie w szybkich przełączeniach lub topologiach o wysokim dv/dt. Ujemne napięcie wyłączenia od −3 do −5 V z zaciskiem Millera zmniejsza ryzyko fałszywego włączenia. - Jak ustawiasz DESAT i czas wygaszania?

Obliczamy na podstawie SOA urządzenia, indukcyjności pasożytniczej i topologii, a następnie weryfikujemy za pomocą przechwytywania oscyloskopu podczas FAT/SAT, aby zapewnić miękkie wyłączanie bez nadmiernej dyssypacji energii. - Czy te sterowniki mogą integrować się z systemami IEC 61850?

Na poziomie systemu, główny kontroler agreguje telemetrię sterownika przez SPI/CAN/optykę i publikuje ją przez IEC 61850 MMS/GOOSE ze zsynchronizowanymi znacznikami czasu. - A co z działaniem w temperaturze >45°C i zapyleniu?

Określamy komponenty klasy przemysłowej, powłoki konformalne i marginesy projektowe termiczne; obudowy osiągają IP54–IP65 zgodnie z wymaganiami dla danego miejsca.

Dlaczego to rozwiązanie działa w Twoich operacjach

Sterowniki bramek SiC zaprojektowane dla wysokiego dv/dt i temperatury odblokowują pełną wydajność tranzystorów MOSFET SiC — wyższą sprawność, mniejsze elementy magnetyczne i stabilną dynamikę — jednocześnie chroniąc urządzenia podczas awarii. W trudnych warunkach Pakistanu i połączeniach z słabą siecią, przekłada się to bezpośrednio na mniejszą liczbę wyłączeń, szybsze zatwierdzenia i niższe koszty eksploatacji.

Połącz się ze specjalistami, aby uzyskać niestandardowe rozwiązania

Współpracuj z Sicarb Tech, aby wspólnie zaprojektować odpowiednią strategię sterowania bramką dla twojego SVG/STATCOM, APF, front-endów VFD i UPS:

- Ponad 10 lat doświadczenia w produkcji SiC

- Badania i rozwój oraz walidacja wspierane przez Chińską Akademię Nauk

- Niestandardowy rozwój produktów w zakresie materiałów R‑SiC, SSiC, RBSiC, SiSiC i modułów mocy SiC

- Transfer technologii i usługi zakładania fabryk — od wykonalności po uruchomienie

- Rozwiązania „pod klucz” od przetwarzania materiałów i podłoży po gotowe systemy i sterowanie

- Sprawdzona historia z ponad 19 przedsiębiorstwami dostarczającymi wymierne zyski w zakresie wydajności i PQ

Uzyskaj bezpłatną konsultację, przegląd projektu i plan uruchomienia na miejscu.

Email: [email protected] | Phone/WhatsApp: +86 133 6536 0038

Metadane artykułu

- Ostatnia aktualizacja: 2025-09-11

- Następna zaplanowana aktualizacja: 2025-12-15

- Przygotowane przez: Zespół inżynierów ds. zastosowań Sicarb Tech

- Odniesienia: IEEE Power Electronics Magazine dotyczące sterowania bramkami WBG; IEC 62477-1; IEC 60664-1; IEEE 519; IEC 61000-3-6; praktyki łączeniowe NTDC/NEPRA

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.