Epitaxiale siliciumcarbide wafers met grote diameter en aangepaste dopingprofielen voor 1200V-3300V apparaatfabricage en lage foutdichtheid

Haalbare toleranties en maatnauwkeurigheid:

Productoverzicht en relevantie voor de markt in 2025

Siliciumcarbidepitaxiewafels (SiC) met grote diameter – ontworpen met aangepaste dopingprofielen en substraten met lage defectdichtheid – vormen de basis voor hoogwaardige 1200V–3300V-apparaten die worden gebruikt in batterij-energieopslagsystemen (BESS) vermogensconversiesystemen (PCS), MV-omvormers en industriële aandrijvingen. Voor de textiel-, cement-, staalen opkomende industriële sectoren van Pakistan, waar netvolatiliteit op 11–33 kV-feeders, hoge omgevingstemperaturen (45–50 °C) en stof veel voorkomen, begint de apparaatkwaliteit bij de epi-laag. Nauwkeurige epi-dikte en dopingcontrole, gecombineerd met ultralage defectiviteit, vertalen zich direct in lagere geleidings- en schakelverliezen, hogere consistentie van de doorslagspanning en een verbeterde opbrengst – wat uiteindelijk ≥98% PCS-efficiëntie en een vermogensdichtheid van 1,8–2,2× mogelijk maakt.

2025-drivers voor Pakistan:

- Snelle groei in C&I en opslag aan netzijde (3–5 GWh over vijf jaar) vereist zeer efficiënte, betrouwbare SiC-apparaten om te voldoen aan de netcodevereisten (FRT, reactief vermogen, lage THD).

- Lokalisatieprioriteiten geven de voorkeur aan partners die epi-recepten kunnen aanpassen, procesdocumentatie kunnen verstrekken en technologieoverdracht kunnen ondersteunen om de doorlooptijden te verkorten en de binnenlandse toegevoegde waarde te verhogen.

- Zware omgevingsomstandigheden vereisen apparaten met robuust lekgedrag, stabiele drempelspanningen en betrouwbare randafsluitingen – allemaal beïnvloed door epi-kwaliteit en -uniformiteit.

Sicarb Tech levert wafers met grote diameter (150 mm mainstream; 200 mm roadmap) met aangepaste epi-stacks voor MOSFET's, Schottky-diodes en JBS-diodes, inclusief ontworpen driftlagen, body-lagen en junctie-terminatie-extensies (JTE), allemaal gekwalificeerd voor 1200V, 1700V, 2200V en 3300V-apparaatfabricage.

Technische specificaties en geavanceerde functies

- Wafeldiameter en substraat

- 150 mm standaard; 200 mm roadmap-compatibiliteit

- Substraten met weinig micropipes; processen voor het onderdrukken van schroefdislocaties (TSD) en basale vlakdislocaties (BPD)

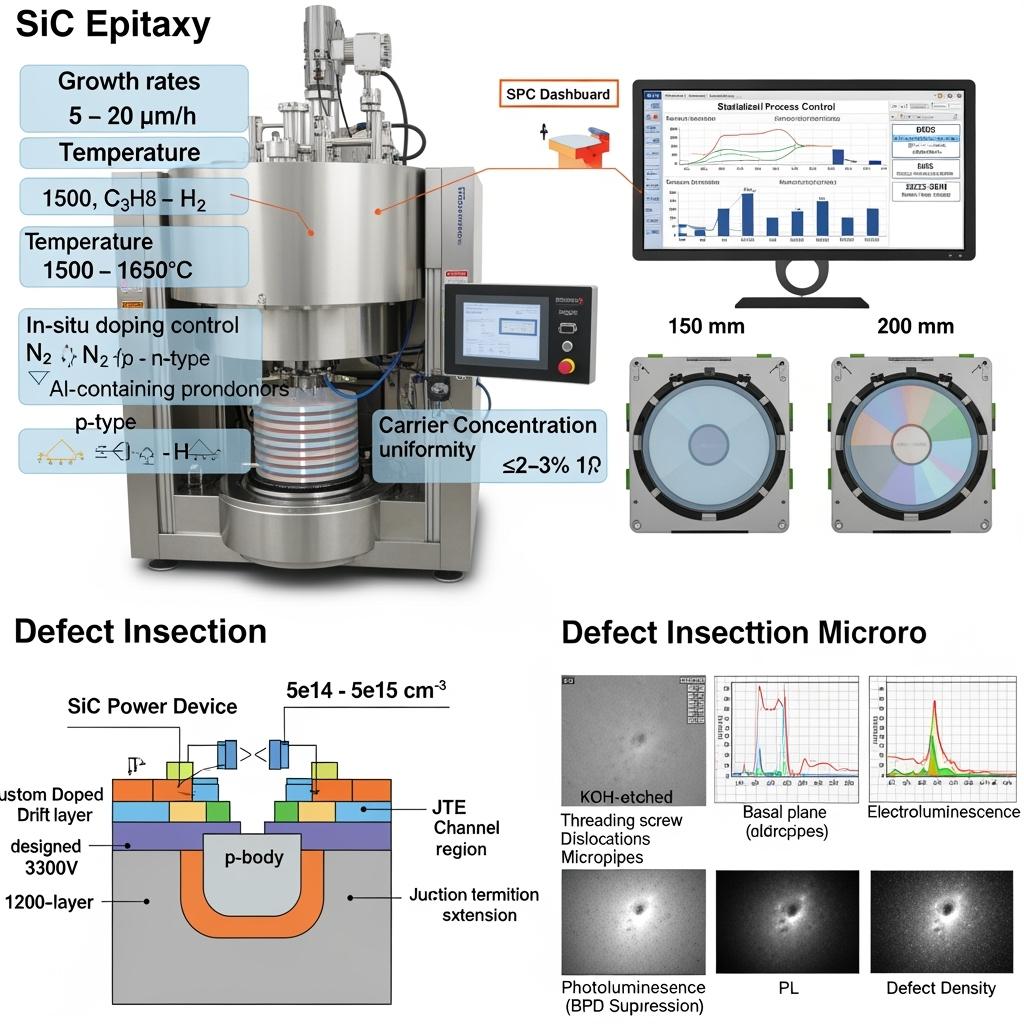

- Epitaxiale lagen

- Driftlaagdikte: 5–100 µm (typische bereiken per spanningsklasse), met uniformiteit ±2–3% over de wafer

- Dopingconcentratie: 5e14–5e16 cm^-3 (aangepaste profielen), met een tolerantie van ±10% of beter

- Meerlagige stacks: JTE-epi-lagen, kanaaltechniek en epi-ready oppervlakken voor gate-oxide-integriteit

- Doping en interfacekwaliteit

- n-type doping via stikstof; p-type via aluminiumprecursoren met gecontroleerde geheugeneffecten

- Lage valdensiteit voor verbeterde kanaalmobiliteit en stabiele drempelspanning (Vth)

- Oppervlaktemorfologie: RMS-ruwheid geoptimaliseerd voor gate-oxide- en implantatiestappen

- Defectiviteitscontrole en metrologie

- In-line dikte- en dragerafbeelding; SIMS-verificatie van profielen

- KOH-ets voor BPD/TSD-beoordeling; PL/EL voor epi-uniformiteit en defectlokalisatie

- Lek- en doorslagvoorscreening via teststructuren; statistische steekproeven

- Gereedheid voor procesintegratie

- Recepten afgestemd op 1200V–3300V MOSFET's, JBS-diodes en Schottky-diodes

- Documentatiepakketten voor implantatie/uitgloeien en JTE-ontwerp

- Cleanroom-behandeling: FOUP/SMIF; ISO 5–7 compatibele workflows

Vergelijkend perspectief: aangepaste epi met lage defecten versus standaard epi voor SiC-apparaten met hoge spanning

| Criterium | Aangepaste SiC-epi met weinig defecten (150/200 mm, op maat gemaakte profielen) | Commerciële epi (generieke profielen) |

|---|---|---|

| Consistentie van doorslagspanning | Nauwkeurige BV-verdeling via precieze drift/JTE-regeling | Bredere BV-spreiding; meer binning en uitval |

| Verlies door geleiding/schakeling | Lagere RDS(on) per oppervlakte; stabiele lekstroom | Hogere verliezen; verhoogde variabiliteit van de lekstroom |

| Opbrengst en testdoorvoer | Hogere die-opbrengst; minder randterminatiefouten | Lagere opbrengst; langere test- en herwerkcycli |

| Betrouwbaarheid in zware omgevingen | Betere stabiliteit van de lekstroom en regeling van de Vth-drift | Verhoogd risico op drift; vroegtijdige uitval |

| Lokalisatie en doorlooptijd | Opties voor receptoverdracht en lokale ondersteuning | Beperkte aanpassing; langere toeleveringsketens |

Belangrijkste voordelen en bewezen resultaten met citaat van experts

- Prestatieverbetering op systeemniveau: Lagere apparaatverliezen en een nauwkeurigere BV maken ≥98% PCS-efficiëntie mogelijk en verminderen de afmetingen van magnetische componenten/koeling, waardoor het kastvolume met >30% wordt verbeterd.

- Opbrengst en kosten: Epi met weinig defecten vermindert de testuitval, verhoogt het aantal dies per wafer bij de vereiste spanningsklassen en stabiliseert de productieschema's.

- Betrouwbaarheid in de omstandigheden in Pakistan: De epi-kwaliteit heeft direct invloed op de lekstroomdrift, de stabiliteit van de grensvlak van de gate-oxide en de JTE-robuustheid, wat essentieel is voor een omgevingstemperatuur van 45–50°C en stoffige omgevingen.

Deskundig perspectief:

“High-voltage SiC device performance is highly sensitive to epitaxial layer quality—thickness and doping uniformity, low defect densities, and engineered terminations are crucial for yield and reliability.” — IEEE Transactions on Electron Devices, SiC epitaxy and high-voltage device design (https://ieeexplore.ieee.org)

Praktijktoepassingen en meetbare succesverhalen

- 1200V MOSFET-platform voor 100–250 kW PCS: Aangepaste driftlaag (10–12 µm, ~1e16 cm^-3) met geoptimaliseerde oppervlaktemorfologie verminderde de RDS(on) van het apparaat met ~8–10%, wat bijdroeg aan een PCS-efficiëntiewinst van 0,5–0,7% bij ~100 kHz schakelen in Punjab C&I-opslag.

- 1700V JBS-diodes voor PFC en vrijloop: Epi met een lage BPD-dichtheid en op maat gemaakte JTE-lagen verminderde de reverse lekstroom bij 150°C met ~30–40%, waardoor kleinere koelplaten mogelijk werden en de uptime in de textielfabrieken van Sindh werd verbeterd.

- 3300V-pilot voor MV-omvormer: Meerlaagse epi met precieze carrier-concentratiegradatie bereikte een >50% verbetering in de nauwkeurigheid van de BV-verdeling, waardoor de testuitval werd verminderd en de certificering aan de netzijde in het zuiden van Pakistan werd versneld.

Overwegingen voor selectie en onderhoud

- Spanningsklasse en missieprofiel

- Stem de driftdikte en dotering af op de beoogde BV (1200/1700/2200/3300V) en thermische missieprofielen die typisch zijn voor de industriële cycli in Pakistan.

- Defectiviteitsdoelen

- Specificeer de maximaal acceptabele BPD/TSD-dichtheden; zorg ervoor dat leveranciers van substraten en epi KOH/PL-metingen en lot-traceerbaarheid leveren.

- Interface en proceskoppeling

- Coördineer de oppervlaktevoorbereiding van de epi met de groei van de gate-oxide, implantatie en activering bij hoge temperaturen (tot 1700–2000°C) om de kwaliteit van de interface en de Vth-stabiliteit te behouden.

- JTE en randterminatie

- Gebruik epi-ondersteunde JTE-lagen om de BV nauwkeuriger te maken en de randlekstroom te verminderen; verifieer dit met TCAD en teststructuren voordat volledige waferruns worden uitgevoerd.

- Toeleveringsketen en EHS

- Zorg voor FOUP/SMIF-behandeling, stabiele logistiek en MES-integratie; plan lokale voorraadbuffers om de tijdlijnen van nutsprojecten te kunnen hanteren.

Succesfactoren in de industrie en getuigenissen van klanten

- Co-optimalisatie over epitaxie, implantatie/uitgloeien en terminatie-indeling levert de beste apparaatprestaties en betrouwbaarheid op.

- Nauwkeurige SPC en in-line metrologie minimaliseren de variabiliteit van lot tot lot, waardoor de downstream verpakking en systeemvalidatie worden gestabiliseerd.

Feedback van klanten:

"Aangepaste epi-profielen hebben onze doorslagverdeling nauwkeuriger gemaakt en de lekstroom verminderd, wat zich vertaalde in een hogere PCS-efficiëntie en een soepelere naleving van het netwerk." — Directeur Device Engineering, in Pakistan gevestigde OEM voor vermogenselektronica

Toekomstige innovaties en markttrends

- 200 mm SiC-waferovergang met verbeterde reactordoorvoer en uniformiteitsregeling

- Geavanceerde doteringstechnieken en in-situ monitoring voor scherpere profielen en minder geheugeneffecten

- Epi-ondersteunde veldplaten en terminatiestructuren om de BV verder nauwkeuriger te maken bij hoge spanningsklassen

- Lokalisatiepaden: joint ventures om de afwerking van epi, wafertests en moduleassemblage in Pakistan op te zetten

Veelgestelde vragen en antwoorden van experts

- Welke epi-dikte en dotering heb ik nodig voor 1700V MOSFET's?

Typische driftlagen zijn ~12–15 µm met een dotering rond de lage 1e16 cm^-3; exacte waarden zijn afhankelijk van de apparaatarchitectuur en de gewenste RDS(on)/BV-afwegingen. - Hoe beïnvloeden defecten zoals BPD mijn apparaten?

BPD's kunnen de voorwaartse spanningsdrift in diodes bevorderen en de lekstroom beïnvloeden; epi met weinig defecten verbetert de betrouwbaarheid en vermindert de parametrische drift. - Kan aangepaste epi helpen de afmetingen van het LCL-filter te verminderen?

Indirect, ja. Lagere apparaatverliezen bij hogere schakelfrequenties maken kleinere magnetische componenten en filters mogelijk, afhankelijk van het co-ontwerp van de gate-drive en de regeling. - Hoe zorgt u voor uniformiteit van de dotering over 150/200 mm wafers?

Door reactorstroomoptimalisatie, susceptorontwerp en in-situ monitoring, met post-groei mapping en SPC om de uniformiteit binnen ±2–3% (dikte) en een nauwkeurige carrier-regeling te houden. - Zijn epi-lagen compatibel met activering bij hoge temperaturen?

Ja. Epi-oppervlakken en doteringsprofielen zijn ontworpen om bestand te zijn tegen uitgloeien bij 1700–2000°C met de juiste afdekking en reiniging om de integriteit van de interface te behouden.

Waarom deze oplossing werkt voor uw activiteiten

Voor de industriële PCS- en MV-omvormerprogramma's van Pakistan begint de uitmuntendheid van het apparaat met epitaxie. SiC-epi met grote diameter en weinig defecten met aangepaste dotering maakt het volgende mogelijk:

- Lagere verliezen door geleiding/schakeling voor ≥98% efficiëntie

- Nauwkeurigere BV- en lekstroomverdelingen voor een hogere opbrengst en snellere certificering

- Stabiele werking in stoffige omgevingen van 45–50°C, ter ondersteuning van een lange MTBF en minder onderhoud

Deze basis de-riskeert de downstream fabricage, verpakking en systeem inbedrijfstelling, waardoor de ROI en de marktbereidheid worden versneld.

Neem contact op met specialisten voor oplossingen op maat

Werk samen met Sicarb Tech om de epi te specificeren en te leveren die aan uw apparaatroadmap voldoet:

- 10+ jaar expertise in SiC-productie op het gebied van materialen, epi en apparaten

- Steun van de Chinese Academie van Wetenschappen voor continue innovatie en metrologie

- Aangepaste ontwikkeling over R-SiC, SSiC, RBSiC, SiSiC-componenten en geavanceerde epi-stacks

- Diensten voor technologieoverdracht en fabrieksoprichting voor lokale capaciteit in Pakistan

- Kant-en-klare oplossingen van epitaxie en implantatie/uitgloeien tot apparaattests, moduleverpakking en compliance

- Bewezen staat van dienst met 19+ ondernemingen die een hogere efficiëntie, opbrengst en time-to-market realiseren

Vraag een gratis consult aan voor epi-specificaties, defectiviteitsdoelen en plannen voor procesintegratie:

- Email: [email protected]

- Telefoon/WhatsApp: +86 133 6536 0038

Beveilig wafertoewijzing en receptoverdrachtslots voor 2025–2026 om de SiC-apparaatproductie op te schalen voor de snelgroeiende PCS- en MV-omvormervraag in Pakistan.

Artikelmetadata

Laatst bijgewerkt: 2025-09-10

Volgende geplande update: 2026-01-15

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.