Siliciumcarbide MOSFET-gate-aandrijfkaarten met actieve Miller-klem, negatieve bias en hoge CMTI-isolatie voor 50-200 kHz-werking

Haalbare toleranties en maatnauwkeurigheid:

Productoverzicht en relevantie voor de markt in 2025

Silicon carbide (SiC) MOSFET gate-drive control boards zijn de hoeksteen voor het ontsluiten van hoogfrequente, zeer efficiënte werking in batterij-energieopslagsystemen (BESS) voor vermogensconversiesystemen (PCS) en MV-omvormers. In de textiel-, cement-, staalen opkomende industriële sectoren van Pakistan moeten omvormers ≥98% efficiëntie, een compacte voetafdruk en stabiele werking leveren op volatiele 11–33 kV-feeders, en dit alles terwijl ze bestand zijn tegen omgevingstemperaturen van 45–50°C en stoffige omgevingen die vaak voorkomen in industrieparken.

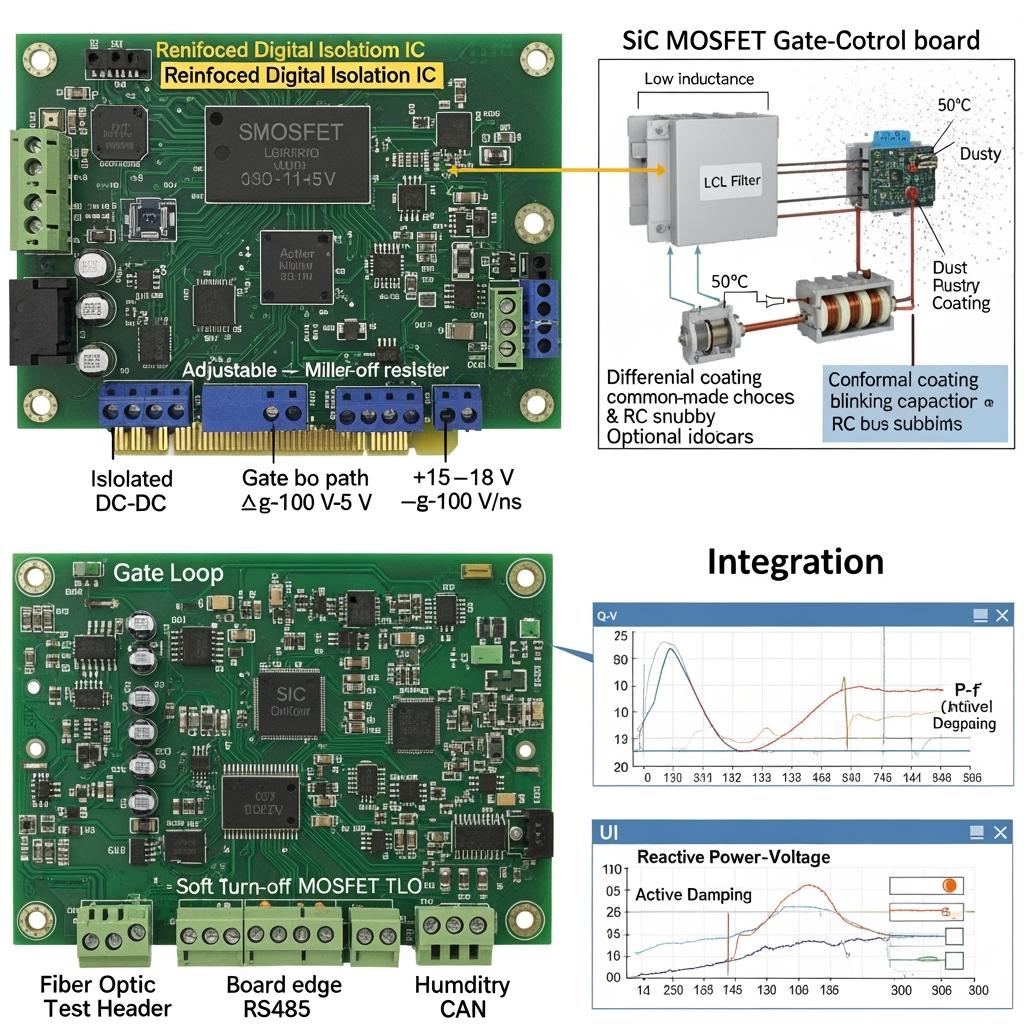

Speciaal gebouwde SiC gate-drive boards maken nauwkeurig, herhaalbaar schakelen bij 50–200 kHz mogelijk door het volgende te combineren:

- Hoge CMTI-versterkte isolatie om snelle dv/dt-randen te tolereren zonder valse trips

- Actieve Miller-klem en configureerbare negatieve gate-bias om parasitaire inschakeling te onderdrukken

- DESAT-bescherming met turn-off in twee niveaus (TLO) voor snelle, gecontroleerde foutafhandeling

- Nauwkeurige propagatievertraging voor symmetrisch half-brugschakelen

- Interfaces die coördineren met PCS-regelingen voor actieve LCL-demping, grid-following (GFL) en grid-forming (GFM) modi, Q–V- en P–f-dalingen en FRT-gedrag

Deze functies vertalen zich in meetbare winsten: kleinere magnetische componenten en filters, kortere inbedrijfstelling op zwakke feeders, minder hinderlijke trips en een verbeterde uptime in zware omstandigheden. Voor implementaties in 2025, aangezien Pakistan 3–5 GWh aan C&I- en netwerkopslag toevoegt, de-riskeren SiC-geoptimaliseerde gate-drive boards programma's en versnellen ze de ROI.

Technische specificaties en geavanceerde functies

- Elektrisch en isolatie

- Gate-spanningsrails: +15 tot +18 V inschakelen, -3 tot -5 V uitschakelen (configureerbare modules)

- Piek aandrijfstroom: 8–30 A klasse voor scherpe randen met beheerde EMI

- Isolatiesterkte: Versterkte isolatie die voldoet aan de relevante IEC/UL; CMTI ≥ 100 V/ns voor 50–200 kHz schakelen

- Propagatievertraging en scheeftrekking: ≤100 ns totale propagatie, ≤30–50 ns kanaal-naar-kanaal scheeftrekking

- Bescherming en foutafhandeling

- DESAT-bescherming met programmeerbare blanking (bijv. 200–800 ns) en zachte turn-off in twee niveaus om overspanning te beperken

- UVLO/OVLO op zowel positieve als negatieve rails; Miller-klemactiveringsdrempels afgestemd op apparaat Cgd

- Programmeerbaar foutvergrendeling, fouttellers en tijdgestempelde logs

- dv/dt-regeling en EMI

- Onafhankelijke inschakel-/uitschakel-Rg; optionele split gate-weerstandsfootprints voor fijnafstemming

- Kelvin-bronpin-routing en ster-aardetopologie om inductieve koppeling te verminderen

- Optionele RC-snubbers en dV/dt-snelheidsregelprofielen geladen via firmware

- Coördinatie en interfaces van de regeling

- Digitale links naar de belangrijkste regelborden die PLL-, GFL/GFM-, Q–V-, P–f-dalingen, actieve LCL-demping en FRT-curven implementeren

- Telemetrie: gate-spanningen, DESAT-gebeurtenissen, temperatuursensoren; optionele glasvezelisolatie voor lawaaierige omgevingen

- Milieubestendigheid

- Omgevingstemperatuur: -40°C tot +105°C; componenten geschikt voor hoge vochtigheid; opties voor conforme coating

- ESD/piekbescherming op I/O; coatingvrijheid gehandhaafd voor kruipweg/vrijheid

Prestatievergelijking: SiC-geoptimaliseerde gate-drives versus conventionele IGBT-georiënteerde drivers

| Criterium | SiC MOSFET gate-drive control boards (50–200 kHz geoptimaliseerd) | Conventionele IGBT-georiënteerde gate-drivers |

|---|---|---|

| Schakelfrequentiecapaciteit | 50–200 kHz met dv/dt-regeling | 5–20 kHz typisch; beperkt bij hogere fsw |

| dv/dt | ≥100 V/ns versterkte isolatie | Lagere CMTI; hoger risico op valse trips |

| Foutbescherming | DESAT + TLO, snel en gecontroleerd | Langzamere OCP; hogere overshoot/belasting |

| Impact van EMI en THD | Schone randen, kleinere LCL-filters | Grotere filters; verhoogde EMI |

| Inbedrijfstelling op zwakke netten | Gecoördineerde actieve demping & netmodi | Langere afstelling; instabiliteitsrisico |

Belangrijkste voordelen en bewezen resultaten met citaat van experts

- Hogere efficiëntie en dichtheid: Stabiele schakeling met hoge frequentie ondersteunt compacte LCL-filters en magnetische componenten, waardoor een PCS-efficiëntie van ≥98% en een volumevermindering van >30% mogelijk is.

- Robuuste bescherming en uptime: DESAT met gecontroleerde TLO beperkt de foutenergie en overshoot, beschermt kostbare SiC-modules en minimaliseert trips.

- Snellere naleving van interconnectie: Ingebouwde coördinatie met droop-regelingen, FRT en actieve demping versnelt de acceptatie van het MV-net.

Deskundig perspectief:

“Gate drivers for wide bandgap transistors must provide fast, deterministic protection and finely controlled slew rates to realize efficiency advantages without compromising reliability.” — IEEE Transactions on Power Electronics, WBG gate-driver design guidance (https://ieeexplore.ieee.org)

Praktijktoepassingen en meetbare succesverhalen

- Punjab 2 MW/4 MWh PCS: SiC-drivers met DESAT/TLO en actieve demping presets maakten een werking van ~100 kHz mogelijk, verhoogden de systeemefficiëntie tot 98,2%, verminderden het kastvolume met 35% en verkortten de inbedrijfstelling met ~30% ondanks zwakke voedingscondities.

- Textielfabriek drives in Sindh: Negatieve bias en Miller-klem elimineerden parasitaire inschakeling, waardoor EMI-trips tijdens zomers van 50°C werden verminderd. De uptime verbeterde en de onderhoudsintervallen werden verlengd.

- MV-omvormer pilot in het zuiden van Pakistan: GFM-coördinatie stabiliseerde de spanning tijdens dips; reactieve ondersteuning (Q–V) voldeed aan de kwaliteitsdoelstellingen voor de stroomvoorziening, waardoor de eerste goedkeuring van de nutsbedrijven werd behaald.

Overwegingen voor selectie en onderhoud

- Apparaatcompatibiliteit en dimensionering

- Match driver piek stroom aan module gate charge (Qg) en gewenste dv/dt; zorg ervoor dat Kelvin source pinnen beschikbaar zijn.

- PCB-lay-out en parasieten

- Houd de gate loop area minimaal; gebruik een strakke koppeling met retourpaden en scheid nodes met hoge dv/dt van logische sporen.

- Bescherming afstemmen

- Stel DESAT-drempels in op basis van datasheet SOA; kalibreer de blanking om ruistriggers te voorkomen en tegelijkertijd echte fouten vast te leggen; controleer de timing van de uitschakeling in twee niveaus.

- Milieubescherming

- Breng een conforme coating aan en selecteer corrosiebestendige afwerkingen; plan het onderhoud van stoffilters voor gekoelde behuizingen.

- Validatieworkflow

- Voer dubbele pulstests uit om Rg en slew af te stellen; correleer DESAT/TLO-gedrag; HIL-test actieve demping en droop-interacties voorafgaand aan full-power tests.

Succesfactoren in de industrie en getuigenissen van klanten

- Co-ontwerp van teams die gate-drive, power layout, LCL-filter en control firmware koppelen, is cruciaal voor stabiliteit bij hoge frequenties en lage THD.

- Parameterpakketten op maat voor nutsbedrijven en voedingssterktes in Pakistan versnellen de uitrol in het veld.

Feedback van klanten:

"De SiC-specifieke gate drivers hebben onze hinderlijke trips geëlimineerd en ons in staat gesteld de schakelfrequentie te verhogen zonder EMI-straffen. Nettests waren eenvoudig." — Lead Power Engineer, Pakistan ESS-integrator

Toekomstige innovaties en markttrends

- Ingebouwde schatting van de junctietemperatuur en stroomdetectie binnen gate drivers voor voorspellend onderhoud

- Adaptieve slew-rate modulatie die reageert op netgebeurtenissen om verliezen en stabiliteit in evenwicht te brengen

- Veilige over-the-air updates met ondertekende parameterpakketten voor door nutsbedrijven gecontroleerde tests

- Lokalisatie van driverassemblage en -test in Pakistan om de doorlooptijden te verkorten en de service te verbeteren

Veelgestelde vragen en antwoorden van experts

- Heb ik negatieve gate bias nodig voor SiC MOSFET's?

Ja, typisch helpt -3 tot -5 V parasitaire inschakeling via Miller-capaciteit te voorkomen tijdens overgangen met hoge dv/dt, vooral in half-bridge poten. - Welke CMTI-classificatie moet ik nastreven?

Streef naar ≥100 V/ns CMTI met versterkte isolatie om valse triggers bij 50–200 kHz schakelen te voorkomen. - Hoe vermindert uitschakeling in twee niveaus de foutbelasting?

TLO voegt een gecontroleerd, langzamer uitschakeltraject in na DESAT-detectie, waardoor VDS-overshoot en di/dt worden beperkt om het apparaat en de module te beschermen. - Kunnen deze drivers helpen bij inbedrijfstelling op zwakke netten?

Ja. Coördinatie met actieve demping en droop-regelingen stabiliseert de stroom en spanning tijdens dips/zwellingen, waardoor de goedkeuring van nutsbedrijven wordt vergemakkelijkt. - Hoe stel ik Rg-waarden af?

Gebruik dubbele pulstests om schakelverliezen en EMI in evenwicht te brengen. Gebruik afzonderlijke inschakel-/uitschakelweerstanden en, indien nodig, gesplitste gate-paden voor fijnere controle.

Waarom deze oplossing werkt voor uw activiteiten

De industriële omgevingen van Pakistan zijn heet, stoffig en uitdagend voor het net. SiC MOSFET gate-drive control boards met actieve Miller-klem, negatieve bias, isolatie met hoge CMTI en DESAT/TLO-bescherming zetten de apparaatvoordelen van SiC om in resultaten in het veld: ≥98% efficiëntie, compacte voetafdruk, minder trips en snelle netconformiteit. Het resultaat is een hogere uptime, lagere LCOE en snellere terugverdientijd in de textiel-, cement-, staal- en opkomende sectoren.

Neem contact op met specialisten voor oplossingen op maat

Werk samen met Sicarb Tech om SiC gate-drive platforms te ontwerpen, valideren en op te schalen:

- 10+ jaar expertise in SiC-productie en applicatie-engineering

- Ondersteund door de Chinese Academie van Wetenschappen voor apparaat-, verpakkings- en besturingsinnovatie

- Maatwerkontwikkeling over R-SiC, SSiC, RBSiC, SiSiC materialen en geavanceerde gate-drive/control stacks

- Technologieoverdracht en fabrieksoprichtingsdiensten om de productie en test in Pakistan te lokaliseren

- Kant-en-klare oplossingen van materialen en apparaten tot gate drives, modules, LCL-filters, koeling en compliance-documentatie

- Bewezen staat van dienst met 19+ bedrijven die een hogere efficiëntie, snellere inbedrijfstelling en betrouwbare werking bereiken

Vraag een gratis consult aan voor driverspecificatie, beschermingsafstemming en inbedrijfstellingsparameterpakketten:

- Email: [email protected]

- Telefoon/WhatsApp: +86 133 6536 0038

Beveilig co-ontwerp- en validatieslots voor 2025–2026 om de naleving van de netcode te versnellen, het EMI-risico te verminderen en implementaties op te schalen in de industriële centra van Pakistan.

Artikelmetadata

Laatst bijgewerkt: 2025-09-10

Volgende geplande update: 2026-01-15

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.