Siliciumcarbide MOSFET-gate driver-circuits met dv/dt-regeling, kortsluitbeveiliging en DESAT-detectie

Haalbare toleranties en maatnauwkeurigheid:

Productoverzicht en relevantie voor de markt in 2025

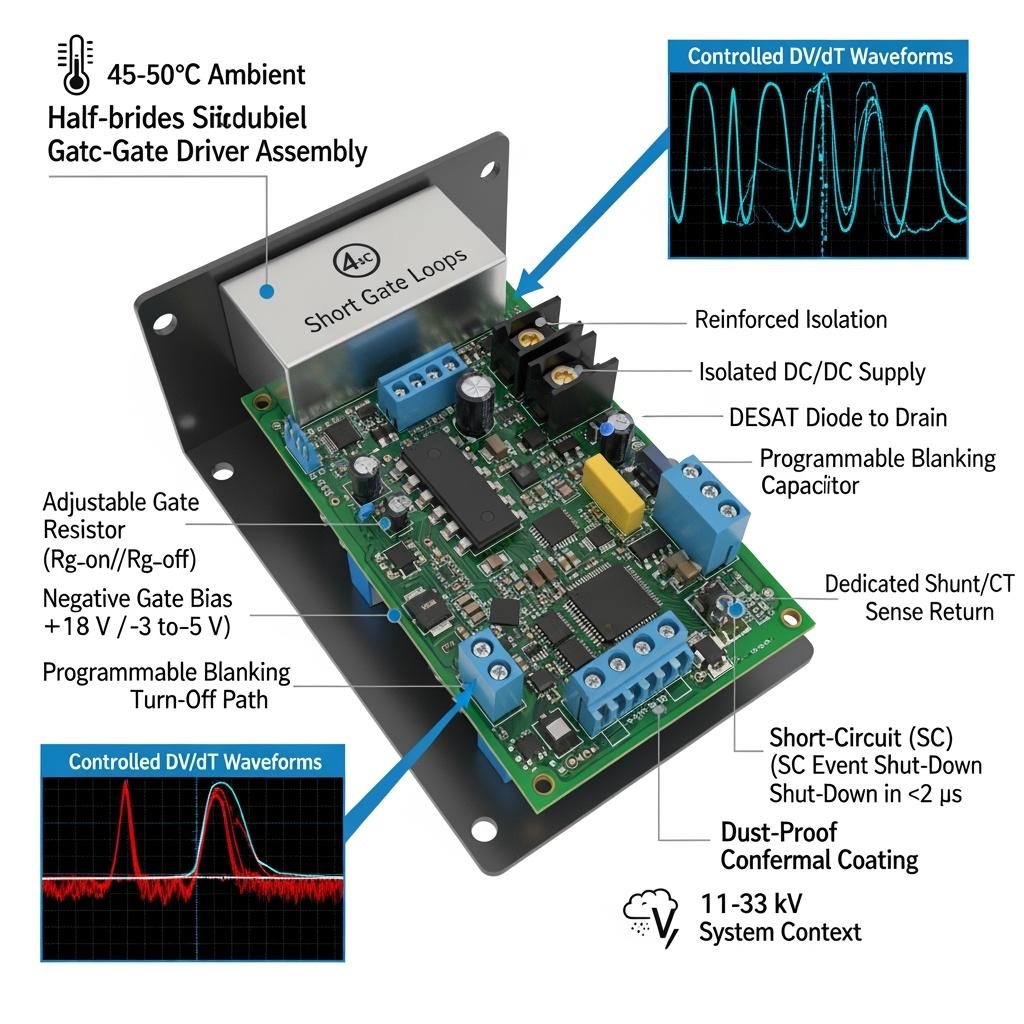

Siliciumcarbide (SiC) MOSFET-gate-drivercircuits zijn de controle-ruggengraat van hoogrendement, hoogvermogensdichtheid. Ze bepalen het schakelgedrag, beheren dv/dt en di/dt en bieden essentiële beschermingsfuncties zoals kortsluituitschakeling en DESAT-detectie. Voor de textiel-, cement- en staal sectoren van Pakistan, waar elektriciteitsruimten te maken hebben met omgevingstemperaturen van 45–50°C en zwevende deeltjes, zijn robuuste gate-drivers essentieel om ≥98,5% omvormerrendement, tot 2× vermogensdichtheid en een lange levensduur te bereiken in 11–33 kV fotovoltaïsche interconnecties en industriële aandrijvingen op distributieniveau.

In 2025 stemmen marktleiders het gate-driverontwerp af op de SiC-apparaatfysica: snelle Miller-plateau-overgangen, smalle veilige werkgebieden tijdens kortsluitingsgebeurtenissen en gevoeligheid voor EMI van hoge dv/dt-randen. Op de toepassing geoptimaliseerde drivers combineren hoge CMTI (>100 V/ns), nauwkeurige inschakel-/uitschakelweerstanden, two-level turn-off (TLO), negatieve gate-bias voor immuniteit en DESAT-detectie met lage latentie. In combinatie met geïsoleerde voeding, versterkte digitale isolatie en PCB-lay-outregels (Kelvin-bron, laag-inductielussen), verminderen deze drivers verliezen, beperken EMI en beschermen modules, zelfs onder stof, hitte en netstoringen die vaak voorkomen in de industriële omgevingen van Pakistan.

Technische specificaties en geavanceerde functies

- Aandrijving en isolatie

- Gate-spanning: +15 tot +20 V inschakelen; -3 tot -5 V uitschakelen (configureerbaar)

- Piekbron-/sinkstroom: 6–30 A-klassen om grote SiC-modules aan te sturen

- Isolatieclassificatie: Versterkte isolatie voor systeem-MV-conformiteit; CMTI ≥ 100 V/ns

- Geïsoleerde DC/DC: Lage common-mode-capaciteit, strakke regulering, undervoltage lockout (UVLO)

- Schakelregeling

- dv/dt-beheer: Onafhankelijke Rg_on/Rg_off, optionele split-gate-aandrijving en actieve Miller-klem

- Two-level turn-off (TLO): Zacht uitschakeltraject om VDS-overschrijding tijdens foutgebeurtenissen te beperken

- Slew-rate-vormgeving: Gate-stroomvormingsnetwerken om verlies en EMI in evenwicht te brengen

- Bescherming en diagnostiek

- DESAT-detectie: Snelle kortsluitdetectie met programmeerbare blanking-tijd en soft-shutdown; <2 µs reactie typisch

- Over-temperatuur input, overstroom via shunt of Rogowski/CT en foutvergrendeling met foutbus signalering

- Gate-bewaking: Open-draad-detectie, gate-source-kortsluitdetectie en UVLO met deterministische foutafhandeling

- Communicatie en besturing

- Interfaces: PWM met deadtime-afdwinging; optionele SPI/UART voor telemetrie (fouten, temperatuur, gebeurtenistellingen)

- Redundante uitschakellijnen voor veiligheid; watchdog/reset-integratie

- Milieu en betrouwbaarheid

- Opties voor conforme coating, corrosiebestendige afwerkingen en uitgebreide temperatuurwerking

- Mechanisch: Voetafdrukken met lage inductie gate-lus, Kelvin-bronconnectiviteit en robuuste connectoren voor veldservice

Beschrijvende vergelijking: SiC-geoptimaliseerde gate-drivers versus conventionele IGBT/silicium-drivers

| Criterium | SiC-geoptimaliseerde gate-driver met dv/dt-regeling en DESAT | Conventionele IGBT/silicium-gate-driver |

|---|---|---|

| Ondersteuning schakelfrequentie | 50–150 kHz met nauwkeurige dv/dt-vormgeving | 5–20 kHz typisch; beperkte dv/dt-regeling |

| CMTI en EMI-robuustheid | ≥100 V/ns met Miller-klem en negatieve bias | Lagere CMTI; hogere gevoeligheid voor valse inschakeling |

| Kortsluitbeveiliging | DESAT met <2 µs reactie en soft-shutdown | Langzamere detectie; hogere belasting tijdens fouten |

| Impact op efficiëntie | Minder schakelverlies, stabiele werking bij hoge omgevingstemperatuur | Hogere verliezen; meer derating bij temperatuur |

| Integratie met SiC-modules | Kelvin-bron, gesplitste gate-weerstanden, snelle bescherming | Vaak ontbreekt SiC-specifieke lay-out en timing |

Belangrijkste voordelen en bewezen resultaten met citaat van experts

- Efficiëntie en dichtheid: dv/dt-regeling en hoge CMTI maken hogere schakelfrequenties (50–150 kHz) mogelijk, waardoor de passieve afmetingen worden verkleind en ≥98,5% efficiëntie wordt ondersteund met compacte filters en koeling.

- Robuuste bescherming: DESAT met TLO voorkomt catastrofale storingen bij kortsluiting of shoot-through-gebeurtenissen, waardoor uitvaltijd en garantie-risico worden verminderd.

- EMI-bestendige werking: Negatieve gate-bias en Miller-klem beperken valse inschakeling, waardoor de stabiliteit wordt gehandhaafd in stoffige, hete elektriciteitsruimten met lange kabelbomen.

- Sneller op de markt: Voorgevalideerde lay-outs, parameterbibliotheken en diagnostische telemetrie verminderen de integratie-inspanning voor 11–33 kV PV- en industriële aandrijvingen.

Deskundig perspectief:

"Het ontwerp van de gate-driver is cruciaal voor het realiseren van de voordelen van wide bandgap-apparaten; hoge CMTI-isolatie, geregelde dv/dt en snelle kortsluitbeveiliging zijn onmisbaar voor betrouwbare SiC-vermogensfasen." — IEEE Power Electronics Society-toepassingsrichtlijnen (ieee.org)

Praktijktoepassingen en meetbare succesverhalen

- Fotovoltaïsche omvormers op distributieniveau (zuidelijk Pakistan): SiC-drivers met DESAT en TLO verminderen schade aan modules door fouten, terwijl dv/dt-vormgeving THD-marge en ≥98,5% efficiëntie opleverde. Systemen realiseerden ~40% reductie in koelvolume als gevolg van stabiele junctietemperaturen.

- VFD's voor textielfabrieken: Negatieve bias en gesplitste gate-weerstanden elimineerden valse inschakeling tijdens snelle transiënten, waardoor ongewenste trips werden verminderd en de uptime van weefgetouwen werd verbeterd in omgevingsomstandigheden van 45–50°C.

- Cement- en staalaandrijvingen: Kortsluitvastheid verbeterd door sub-2 µs DESAT-actie, waardoor vertragingen in de bescherming van IGBT's en bijbehorende nevenschade werden verminderd. Onderhoudsoproepen daalden meetbaar tijdens de piekbelastingen in de zomer.

Overwegingen voor selectie en onderhoud

- Apparaatkoppeling

- Match driverstroom en spanningszwaai met module gate-lading en gewenste schakelsnelheid; zorg voor Kelvin-bronbeschikbaarheid.

- Valideer negatief biasniveau om immuniteit en oxide-spanningslimieten in evenwicht te brengen.

- Bescherming afstemmen

- Stel DESAT-drempel en blanking-tijd in per module-eigenschappen en verwachte strooi-inductie.

- Implementeer TLO-weerstandsafmetingen om VDS-overschrijding te beperken zonder de energieafvoer te verlengen.

- PCB/lay-out

- Minimaliseer lusinductie; scheid vermogens- en logische massa's; gebruik een speciale retour voor DESAT- en detectielijnen.

- Plaats DC/DC en isolator weg van knooppunten met hoge di/dt; handhaaf kruipafstand/speling die geschikt is voor MV-systemen.

- Milieubescherming

- Breng conforme coating aan voor stof; specificeer componenten voor hoge temperaturen; controleer de werking bij 45–50°C omgevingstemperatuur.

- Verificatie

- Voer dubbele pulstests uit om dv/dt af te stemmen; kortsluitingstests om TSC-reactie te valideren; EMC-pre-compliance voor geleide/uitgestraalde emissies.

Succesfactoren in de industrie en getuigenissen van klanten

- Co-ontwerp met moduleverpakking en LCL-filterteams stemt dv/dt-doelen af op EMI- en THD-doelen, waardoor herontwerplussen worden verminderd.

- Vroege validatie van het missieprofiel vermindert over-engineering en kosten en handhaaft tegelijkertijd de betrouwbaarheid.

Feedback van klanten:

"Het integreren van snelle DESAT en two-level turn-off in onze SiC-halfbruggen elimineerde veldfouten door zeldzame kortsluitingsgebeurtenissen. dv/dt-afstemming verbeterde de EMI-headroom zonder de efficiëntie op te offeren." — Lead power engineer, C&I PV-integrator in Sindh

Toekomstige innovaties en markttrends

- Digitale gate-drivers met adaptieve dv/dt-regeling op basis van real-time stroom- en temperatuurdetectie

- Geïntegreerde conditiebewaking (SOH-metrieken) voor gate-lading en drempelwaardedrift-tracking

- Hogere CMTI-isolatietechnologieën en lagere common-mode-capaciteit voor multi-MW MV-systemen

- Referentieontwerpen op maat voor de MV PV-pijplijn van Pakistan (>5 GW) met lokale productiesteun

Veelgestelde vragen en antwoorden van experts

- Waarom negatieve gate-bias gebruiken met SiC MOSFET's?

Om valse inschakeling door Miller-koppeling bij hoge dv/dt te voorkomen. Typische waarden zijn -3 tot -5 V, geselecteerd per apparaatlimiet en EMI-doelen. - Hoe snel moet DESAT-bescherming zijn?

Richt op totale reactietijden van minder dan ~2 µs vanaf het begin van de fout tot de stroomonderbreking, met soft-shutdown om overspanningsbelasting te beperken. - Wat is two-level turn-off en waarom gebruiken?

TLO introduceert een gecontroleerde, zachtere uitschakeling tijdens fouten om VDS-overschrijding en strooi-inductieve ringing te verminderen, waardoor de module en gate-oxide worden beschermd. - Hoe stem ik dv/dt af zonder efficiëntie te verliezen?

Gebruik gesplitste Rg_on/Rg_off, lay-out om inductie te verminderen en optioneel gate-stroomvorming; herhaal via dubbele pulstests om EMI en schakelverlies in evenwicht te brengen. - Kunnen deze drivers betrouwbaar werken bij 45–50°C met stof?

Ja. Met conforme coating, gedegradeerde componenten en de juiste luchtstroom of afdichting behouden drivers de stabiliteit en beschermingsprestaties.

Waarom deze oplossing werkt voor uw activiteiten

Deze op SiC gerichte gate-drivercircuits leveren de controleprecisie en beschermingssnelheid die nodig zijn voor de MV-interconnecties en zware industriële aandrijvingen van Pakistan. Ze maken hogere schakelfrequenties mogelijk voor compacte LCL-filters, stabiliseren de werking in hete, stoffige omgevingen en beschermen tegen beschadigende fouten - waardoor ≥98,5% efficiëntie, tot 2× vermogensdichtheid en een lange levensduur worden ontgrendeld in textiel-, cement- en staaltoepassingen.

Neem contact op met specialisten voor oplossingen op maat

Versnel uw SiC-vermogensfase met deskundig driverontwerp en -validatie:

- 10+ jaar SiC-productie-expertise en applicatie-engineering

- Ondersteuning van een toonaangevend onderzoeksecosysteem dat innovatie stimuleert in isolatie, bescherming en EMI-regeling

- Maatwerk productontwikkeling voor R-SiC-, SSiC-, RBS

- Technologieoverdracht en diensten voor de fabrieksopstelling voor lokale assemblage en testen van drivers

- Kant-en-klare oplossingen, van apparaten en drivers tot filters, koeling en naleving

- Bewezen resultaten met 19+ ondernemingen die efficiëntie, betrouwbaarheid en een snellere time-to-market leveren

Vraag een gratis consult aan en een op maat gemaakt specificatiepakket voor gate drivers:

- Email: [email protected]

- Telefoon/WhatsApp: +86 133 6536 0038

Boek nu uw ontwikkelingsslots voor 2025–2026 om co-design, EMC-validatie en veldproeven veilig te stellen die aansluiten bij de MV PV- en industriële drive-uitrol.

Artikelmetadata

Laatst bijgewerkt: 2025-09-10

Volgende geplande update: 2026-01-15

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.