SiC MOSFET에 최적화된 고주파, 고온 게이트 드라이버(절연, 높은 dv/dt 내성)

공유

2025년 파키스탄의 고효율 컨버터를 위한 게이트 드라이브 신뢰성

파키스탄의 섬유, 시멘트 및 강철 신드 및 발루치스탄에서 재생 에너지 용량이 확장되는 동안, 전력 품질 업그레이드 및 전력화가 가속화되고 있습니다. SVG/STATCOM, APF, 고주파 드라이브, UPS 및 산업용 전원 공급 장치에서 실리콘 카바이드(SiC) MOSFET의 효율성과 속도를 최대한 실현하려면 게이트 드라이버가 매우 중요합니다. 강화된 절연 및 높은 dv/dt 내성을 갖춘 고주파, 고온 SiC에 최적화된 게이트 드라이버는 잘못된 턴온을 방지하고, 스위칭 손실을 최소화하며, 45°C 초과 주변 온도, 먼지 및 습도에서 안정적인 작동을 보장합니다.

Sicarb Tech는 견고한 절연, 넓은 공통 모드 과도 내성(CMTI), 정밀한 밀러 제어 및 프로그래밍 가능한 턴온/턴오프 다이내믹스를 특징으로 하는 SiC에 최적화된 게이트 구동 솔루션을 설계하고 공급합니다. 중국 과학원의 지원을 받아, 당사의 플랫폼은 다중 레벨 토폴로지 및 IEC 61850 모니터링 시스템에 원활하게 통합되어 NTDC/NEPRA 상호 연결을 위한 시운전 주기를 단축하고 장기적인 신뢰성을 향상시킵니다.

기술 사양 및 고급 기능

- 절연 및 노이즈 내성

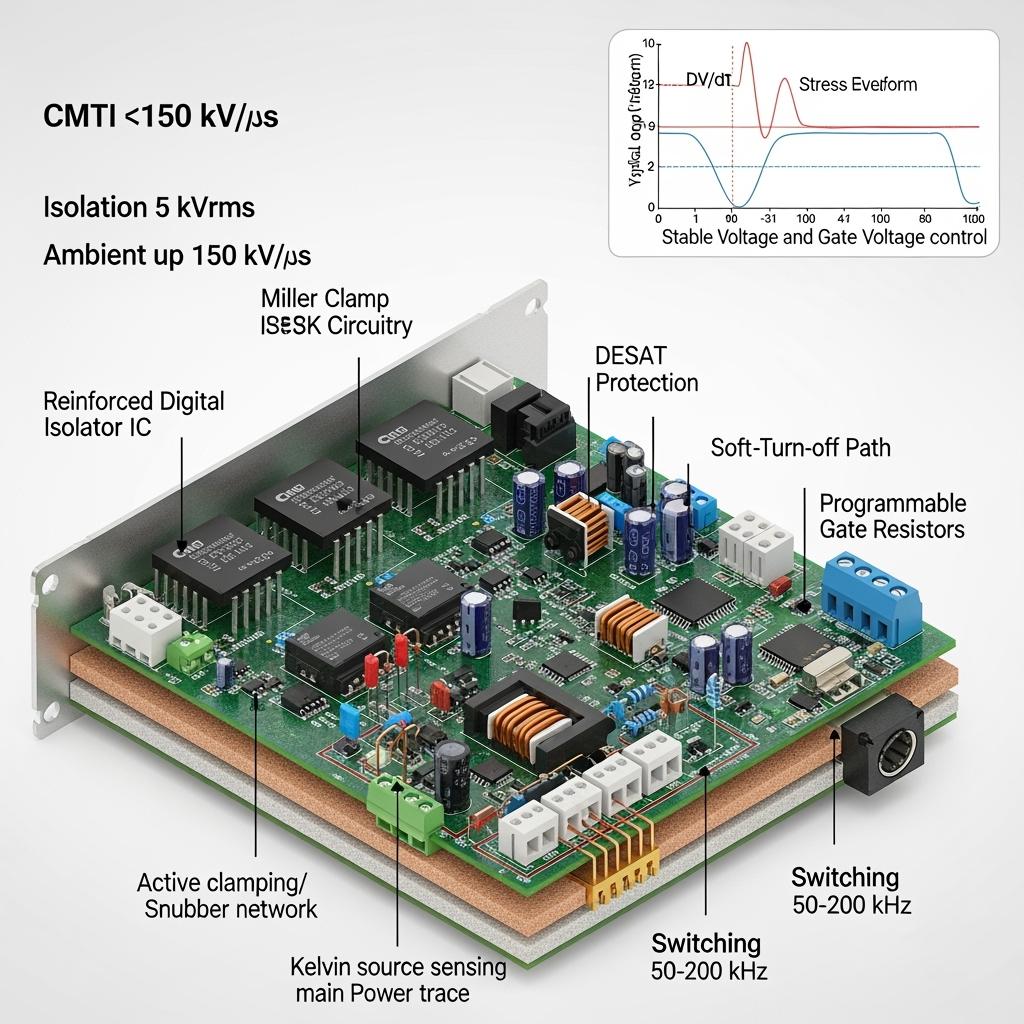

- 최대 5 kVrms의 강화 절연; IEC 60664-1에 맞게 설계된 크리피지/클리어런스

- 데이터 손상 없이 빠른 SiC 스위칭 에지를 허용하기 위한 CMTI ≥150 kV/µs

- 변전소 및 공장의 긴 노이즈 케이블 런을 위한 광섬유 또는 차동 링크 옵션

- 게이트 제어 및 보호

- EMI 및 오버슈트 제어를 위한 프로그래밍 가능한 게이트 저항 및 분할 RG(턴온/턴오프)

- 잘못된 턴온을 방지하기 위한 밀러 클램프 및 음의 게이트 바이어스(예: +18 V / −3 ~ −5 V)

- 소프트 턴오프가 있는 DESAT 과전류 보호; 단락 내성 조정

- 액티브 게이트 제어 프로파일: 손실 및 EMI의 균형을 맞추기 위한 di/dt 및 dv/dt 쉐이핑

- 전력 및 열

- 절연 바이어스 공급 ±18 V 클래스, 채널당 3–6 W; SiC MOSFET 요구 사항에 일치하는 UVLO 임계값

- 최대 105°C 주변 온도에서 작동; 산업 등급에 맞춰진 접합 온도에 대한 구성 요소 정격

- 낮은 기생 인덕턴스 및 켈빈 소스 리턴을 갖춘 효율 최적화 레이아웃

- 타이밍 및 진단

- 다중 레벨 스택의 경우 전파 지연 <100 ns, 채널 간 매칭 ≤20 ns

- SPI/CAN/광학 링크를 통한 고장 래칭, 이벤트 타임스탬핑 및 상태 모니터링

- 메인 제어 보드(시스템 레벨 인터페이스)를 통해 IEC 61850 게이트웨이에 통합할 준비 완료

- 규정 준수 및 신뢰성

- IEC 62477-1(컨버터 안전) 및 산업용 EMC 요구 사항을 충족하도록 설계됨

- 시멘트 먼지 및 해안 습도에 대한 컨포멀 코팅 옵션; 시스템 레벨에서 IP 등급 인클로저 사용 가능

가혹하고 고속 스위칭 환경에서 SiC에 최적화된 게이트 드라이버가 기존 드라이버보다 성능이 뛰어난 이유

| 설계 초점 | SiC에 최적화된 절연 게이트 드라이버(이 솔루션) | 기존 IGBT 시대 드라이버 | 파키스탄에서의 운영 영향 |

|---|---|---|---|

| dv/dt 및 CMTI | ≥150 kV/µs CMTI; 빠른 에지에 강함 | 25–50 kV/µs; 잘못된 트리거에 취약함 | 약한 그리드 이벤트 및 노이즈가 많은 변전소에서의 안정성 |

| 게이트 제어 | 분할 RG, 밀러 클램프, −Vge 턴오프, 액티브 제어 | 고정 RG, 제한된 클램프 옵션 | 낮은 EMI, 더 적은 불필요한 트립, 더 나은 효율성 |

| 보호 | 소프트 턴오프가 있는 DESAT, 빠른 단락 응답 | 더 느린 OC 감지; 더 가혹한 턴오프 | 고가의 SiC 모듈을 보호하고 가동 중단 시간을 줄입니다. |

| 열 정격 | 최대 105°C 주변 온도; 고신뢰성 구성 요소 | 일반적인 70–85°C | 45°C 초과 주변 온도 및 먼지가 많은 공장에서 신뢰할 수 있습니다. |

| 동기화 | 다중 레벨 토폴로지에 대한 엄격한 지연 매칭 | 느슨한 매칭 | 균형 잡힌 스위칭, 순환 전류 감소 |

주요 장점 및 입증된 이점

- 고주파수(50–200 kHz)에서 효율성 및 EMI 균형: 프로그래밍 가능한 게이트 프로파일은 EMC를 희생하지 않고 스위칭 손실을 줄입니다.

- 온도에서의 신뢰성: 뜨겁고 먼지가 많은 시멘트 및 강철 환경에서 안정적인 작동은 디레이팅 및 가동 중단을 최소화합니다.

- SiC에 맞게 조정된 보호: 빠른 DESAT 및 소프트 턴오프는 고장 및 그리드 이벤트 동안 장치 스트레스를 줄입니다.

- 더 빠른 시운전: 통합 진단 및 표준화된 인터페이스는 FAT/SAT 및 NTDC/NEPRA 승인을 가속화합니다.

전문가 인용문:

“Gate drivers are the linchpin for realizing SiC’s promise—robust isolation, high CMTI, and precise gate shaping are essential to avoid EMI issues and unlock efficiency gains.” — Interpreted from IEEE Power Electronics Magazine perspectives on WBG gate driving (https://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6161321)

실제 응용 분야 및 측정 가능한 성공 사례

- 신드 풍력 발전소의 SVG/STATCOM(복합): SiC에 최적화된 드라이버로 업그레이드하여 반응 단계 응답을 <10ms로 개선하고 스위칭 손실을 ~12% 줄여 보상 체인 효율을 98% 이상으로 높였습니다.

- 파이살라바드의 섬유 VFD 프런트 엔드 개조: 게이트 쉐이핑은 EMI 유도 트립을 70% 줄였고 주파수를 20kHz에서 60kHz로 높여 자성체를 ~25% 축소했습니다.

- 카라치의 강철 APF: 음의 게이트 바이어스 및 밀러 클램프는 EAF 과도 현상 동안 잘못된 턴온을 제거했고, THD는 필터 재조정 없이 IEEE 519 한계 내에서 안정화되었습니다.

- KP의 시멘트 공장 보조 장치: 컨포멀 코팅된 게이트 드라이버 어셈블리는 12개월 동안 드라이버 관련 고장 이벤트가 <0.5%로 먼지 시즌 동안 가동 시간을 유지했습니다.

선택 및 유지 관리 고려 사항

- 전기적 호환성

- 장치 게이트 전하 및 원하는 스위칭 속도에 맞게 드라이버 출력 전류(2–10 A 피크)를 일치시킵니다.

- 게이트 산화물을 과도하게 스트레칭하지 않고 밀러 턴온을 억제하기 위해 음의 게이트 바이어스 레벨을 선택합니다.

- UVLO 임계값이 MOSFET 요구 사항(+/− 레일)에 맞는지 확인합니다.

- 절연 및 레이아웃

- MV 스택에 강화 절연을 선택하고, 현지 오염 정도에 대한 크리피지/클리어런스를 확인합니다.

- 기생 인덕턴스 및 측정 오류를 최소화하기 위한 켈빈 소스 리턴 라우팅

- 보호 및 감지

- 장치 특성 및 토폴로지(NPC/ANPC/MMC)에 맞게 DESAT 임계값 설정 및 블랭킹 시간 조정

- 열 폴드백을 위해 다이 근처에 NTC/RTD 감지를 통합하고, 메인 컨트롤러로의 고장 전파 경로를 확인합니다.

- 환경적 견고성

- 먼지/습한 현장에서 컨포멀 코팅 및 개스킷 처리된 인클로저를 지정합니다.

- 드라이버 및 게이트 저항 주변의 공기 흐름 또는 액체 냉각 경로를 검증합니다.

- 수명 주기 및 예비 부품

- 펌웨어/구성 백업을 유지하고, 중요한 피더에 대해 보정된 예비 부품을 보관합니다.

- 운영 프로파일이 발전함에 따라 매년 매개변수 조정을 검토할 계획을 세웁니다.

산업 성공 요인 및 고객 사용후기

- 스위칭 주파수, EMI 목표 및 그리드 규정 준수를 맞추기 위해 EPC/통합업체와 초기 공동 설계를 진행합니다.

- 시운전 중 현장 오실로그래피를 통해 RG 분할, 클램프 임계값 및 블랭킹 시간을 최종 결정합니다.

- 진단을 해석하고 매개변수 무결성을 유지하기 위해 O&M 팀에 대한 현장 교육을 실시합니다.

고객의 소리(합성):

"SiC 특정 드라이버를 채택한 후, EMI 페널티 없이 더 높은 주파수로 추진하고 그리드 플리커 이벤트 동안 불필요한 트립을 제거했습니다." — 펀자브 섬유 클러스터, 전기 유지보수 책임자

미래 혁신 및 2025+ 시장 동향

- SiC 전력 모듈에 통합된 드라이버: 더 짧은 루프 인덕턴스, 내장형 감지 및 더 스마트한 보호

- 스위칭 손실을 동적으로 최소화하기 위해 실시간 장치 온도 및 전류를 사용하는

- MMC 기반 유틸리티 컨버터를 위한 높은 CMTI(>200 kV/µs) 및 낮은 지터의 디지털 절연

- 중요 인프라를 위해 IEC 62443을 준수하는 사이버 보안 진단 채널

일반적인 질문 및 전문가 답변

- 50–100 kHz 스위칭에서 SiC에 권장되는 CMTI는 무엇입니까?

≥100–150 kV/µs가 권장되며, 당사 설계는 약전력망 및 EAF 환경에서 여유를 위해 ≥150 kV/µs를 목표로 합니다. - SiC MOSFET에 네거티브 게이트 바이어스가 필요합니까?

특히 고속 스위칭 또는 높은 dv/dt 토폴로지에서 그렇습니다. 밀러 클램프를 사용한 -3 ~ -5 V 턴오프는 오작동 위험을 줄입니다. - DESAT 및 블랭킹 시간을 어떻게 설정합니까?

장치 SOA, 기생 인덕턴스 및 토폴로지를 기반으로 계산한 다음, FAT/SAT 동안 오실로스코프 캡처로 검증하여 과도한 에너지 손실 없이 소프트 턴오프를 보장합니다. - 이러한 드라이버는 IEC 61850 시스템과 통합될 수 있습니까?

시스템 수준에서, 주 제어기는 SPI/CAN/광학을 통해 드라이버 원격 측정 데이터를 집계하고, 동기화된 타임스탬프와 함께 IEC 61850 MMS/GOOSE를 통해 게시합니다. - 45°C 초과 및 먼지 환경에서의 작동은 어떻습니까?

산업 등급 부품, 컨포멀 코팅 및 열 설계 여유를 지정합니다. 인클로저는 현장 요구 사항에 따라 IP54–IP65를 달성합니다.

이 솔루션

높은 dv/dt 및 온도에 맞게 설계된 SiC 게이트 드라이버는 SiC MOSFET의 완전한 성능(더 높은 효율, 더 작은 자성체 및 안정적인 동적 특성)을 발휘하는 동시에 고장 시 장치를 보호합니다. 파키스탄의 가혹한 환경과 약전력망 상호 연결에서 이는 직접적으로 더 적은 트립, 더 빠른 승인 및 더 낮은 수명 비용으로 이어집니다.

맞춤형 솔루션을 위해 전문가와 연결

SVG/STATCOM, APF, VFD 프론트 엔드 및 UPS에 적합한 게이트 구동 전략을 공동 설계하려면 Sicarb Tech와 협력하십시오.

- 10년 이상의 SiC 제조 전문 지식

- 중국 과학원 지원 R&D 및 검증

- R‑SiC, SSiC, RBSiC, SiSiC 재료 및 SiC 전력 모듈 전반의 맞춤형 제품 개발

- 기술 이전 및 공장 설립 서비스 - 타당성 검토부터 시운전까지

- 재료 처리 및 기판에서 완제품 및 제어에 이르기까지 턴키 솔루션

- 측정 가능한 효율성 및 PQ 향상을 제공하는 19개 이상의 기업과 입증된 실적

무료 상담, 설계 검토 및 현장 시운전 계획을 받으십시오.

Email: [email protected] | Phone/WhatsApp: +86 133 6536 0038

문서 메타데이터

- 최종 업데이트: 2025-09-11

- 다음 예약 업데이트: 2025-12-15

- 작성자: Sicarb Tech 애플리케이션 엔지니어링 팀

- 참고 자료: WBG 게이트 구동에 관한 IEEE 전력 전자 매거진; IEC 62477-1; IEC 60664-1; IEEE 519; IEC 61000-3-6; NTDC/NEPRA 상호 연결 관행

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.