dv/dt 제어, 단락 회로 보호 및 DESAT 감지 기능을 갖춘 실리콘 카바이드 MOSFET 게이트 드라이버 회로

공유

제품 개요 및 2025년 시장 관련성

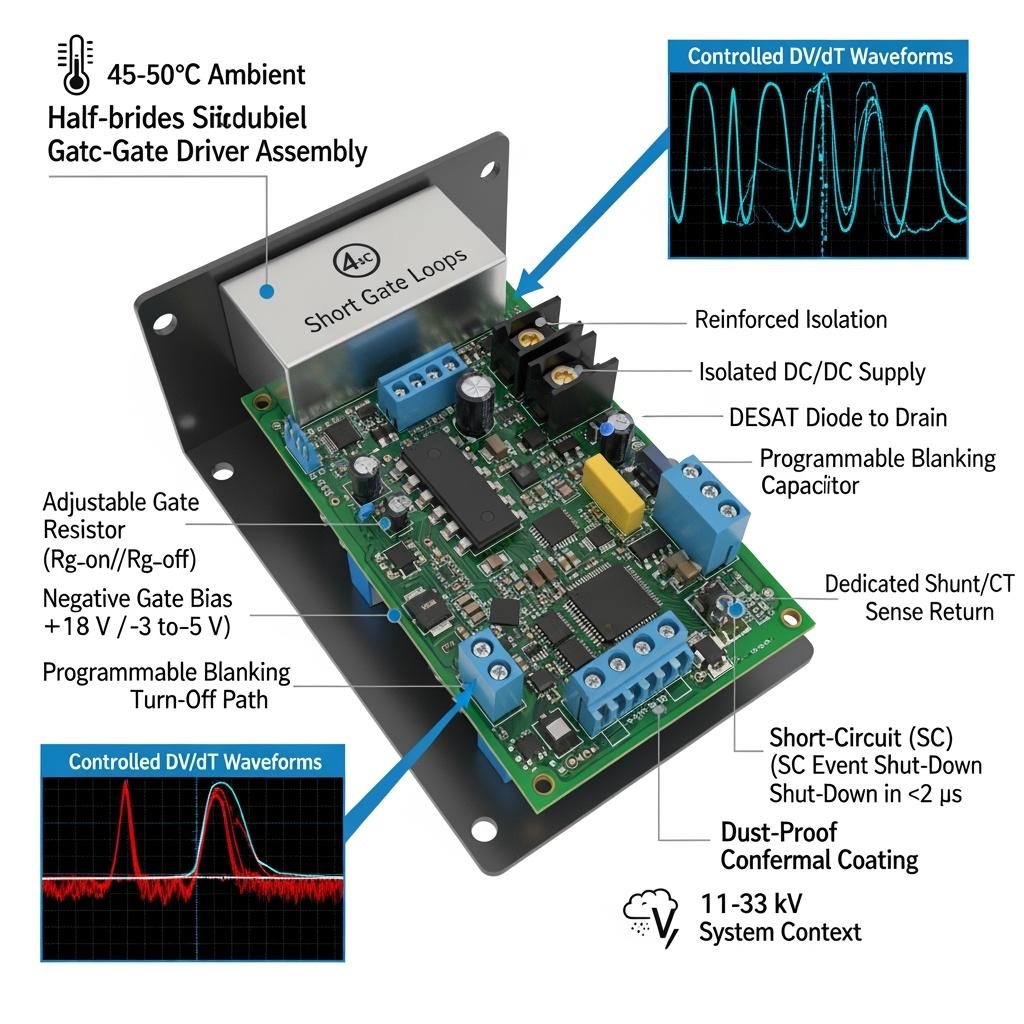

실리콘 카바이드(SiC) MOSFET 게이트 드라이버 회로는 고효율, 고밀도 전력 스테이지의 제어 백본입니다. 스위칭 동작을 결정하고, dv/dt 및 di/dt를 관리하며 단락 차단 및 DESAT 감지와 같은 중요한 보호 기능을 제공합니다. 파키스탄의 섬유, 시멘트 및 강철 전기실이 45–50°C 주변 온도와 공기 중 먼지에 직면하는 부문에서 강력한 게이트 드라이버는 11–33kV 배전 수준의 광전지 상호

2025년, 시장 선두 주자들은 SiC 소자 물리에 맞춰 게이트 드라이버 설계를 조정하고 있습니다. 즉, 빠른 밀러 평탄부 전이, 단락 시 좁은 안전 동작 영역, 높은 dv/dt 에지에서 발생하는 EMI에 대한 민감성 등을 고려합니다. 애플리케이션에 최적화된 드라이버는 높은 CMTI(>100V/ns), 정밀한 턴온/턴오프 게이트 저항, 2단계 턴오프(TLO), 면역을 위한 음의 게이트 바이어스, 낮은 지연 시간의 DESAT 감지를 결합합니다. 절연 전원, 강화 디지털 절연, PCB 레이아웃 규칙(켈빈 소스, 낮은 인덕턴스 루프)과 함께 이러한 드라이버는 손실을 줄이고, EMI를 완화하며, 파키스탄 산업 환경에서 흔히 발생하는 먼지, 열, 그리드 장애에서도 모듈을 보호합니다.

기술 사양 및 고급 기능

- 드라이브 및 절연

- 게이트 전압: +15~+20V 턴온, -3~-5V 턴오프(구성 가능)

- 피크 소스/싱크 전류: 대형 SiC 모듈 구동을 위한 6~30A 클래스

- 절연 등급: 시스템 MV 규정 준수를 위한 강화 절연, CMTI ≥ 100V/ns

- 절연 DC/DC: 낮은 공통 모드 커패시턴스, 정밀한 조정, 저전압 록아웃(UVLO)

- 스위칭 제어

- dv/dt 관리: 독립 Rg_on/Rg_off, 선택적 분할 게이트 드라이브, 액티브 밀러 클램프

- 2단계 턴오프(TLO): 고장 시 VDS 오버슈트를 제한하는 소프트 턴오프 경로

- 슬루율 성형: 손실 및 EMI의 균형을 맞추기 위한 게이트 전류 성형 네트워크

- 보호 및 진단

- DESAT 감지: 프로그래밍 가능한 블랭킹 시간 및 소프트 셧다운을 통한 빠른 단락 감지, 일반적인 반응 시간 <2µs

- 과열 입력, 션트 또는 Rogowski/CT를 통한 과전류, 고장 버스 신호와 함께 고정 고장

- 게이트 모니터링: 개방선 감지, 게이트-소스 단락 감지, 결정론적 고장 처리를 통한 UVLO

- 통신 및 제어

- 인터페이스: 데드타임 적용 PWM, 원격 측정(고장, 온도, 이벤트 수)을 위한 선택적 SPI/UART

- 안전을 위한 중복 비활성화 라인, 워치독/리셋 통합

- 환경 및 신뢰성

- 컨포멀 코팅 옵션, 내식성 마감, 확장된 온도 작동

- 기계적: 낮은 인덕턴스 게이트 루프 풋프린트, 켈빈 소스 연결, 현장 서비스를 위한 견고한 커넥터

설명 비교: SiC 최적화 게이트 드라이버 vs 기존 IGBT/실리콘 드라이버

| 기준 | dv/dt 제어 및 DESAT 기능을 갖춘 SiC 최적화 게이트 드라이버 | 기존 IGBT/실리콘 게이트 드라이버 |

|---|---|---|

| 스위칭 주파수 지원 | 정밀한 dv/dt 성형으로 50~150kHz | 일반적인 5~20kHz, 제한된 dv/dt 제어 |

| CMTI 및 EMI 견고성 | 밀러 클램프 및 음의 바이어스로 ≥100V/ns | 낮은 CMTI, 가짜 턴온에 대한 높은 민감도 |

| 단락 보호 | <2µs 반응 및 소프트 셧다운을 통한 DESAT | 더 느린 감지, 고장 시 더 높은 스트레스 |

| 효율성 영향 | 낮은 스위칭 손실, 높은 주변 온도에서 안정적인 작동 | 더 높은 손실, 온도에서 더 많은 디레이팅 |

| SiC 모듈과의 통합 | 켈빈 소스, 분할 게이트 저항, 빠른 보호 | SiC 특정 레이아웃 및 타이밍이 없는 경우가 많음 |

주요 장점 및 입증된 이점(전문가 인용문 포함)

- 효율성 및 밀도: dv/dt 제어 및 높은 CMTI는 더 높은 스위칭 주파수(50~150kHz)를 가능하게 하여 수동 소자 크기를 줄이고, 소형 필터 및 냉각으로 ≥98.5% 효율성을 지원합니다.

- 강력한 보호: DESAT와 TLO는 단락 또는 관통 이벤트 시 치명적인 고장을 방지하여 가동 중단 시간과 보증 위험을 줄입니다.

- EMI 탄력적 작동: 음의 게이트 바이어스 및 밀러 클램프는 가짜 턴온을 완화하여 먼지가 많고 뜨거운 전기실에서 긴 케이블 하네스를 사용하더라도 안정성을 유지합니다.

- 더 빠른 시장 출시 시간: 사전 검증된 레이아웃, 매개변수 라이브러리, 진단 원격 측정은 11~33kV PV 및 산업용 드라이브의 통합 노력을 줄입니다.

전문가의 관점:

"게이트 드라이버 설계는 광대역 갭 소자의 장점을 실현하는 데 매우 중요합니다. 높은 CMTI 절연, 제어된 dv/dt, 빠른 단락 보호는 안정적인 SiC 전력 스테이지에 필수적입니다." — IEEE 전력 전자 학회 애플리케이션 가이드(ieee.org)

실제 응용 분야 및 측정 가능한 성공 사례

- 배전 레벨 PV 인버터(파키스탄 남부): DESAT 및 TLO를 갖춘 SiC 드라이버는 고장 관련 모듈 손상을 줄이는 동시에 dv/dt 성형으로 THD 여유를 확보하고 ≥98.5% 효율성을 달성했습니다. 시스템은 안정적인 접합 온도 덕분에 냉각 부피를 ~40% 줄였습니다.

- 섬유 공장 VFD: 음의 바이어스 및 분할 게이트 저항은 빠른 과도 현상 동안 가짜 턴온을 제거하여 45~50°C 주변 조건에서 불필요한 트립을 줄이고 직기 가동 시간을 개선했습니다.

- 시멘트 및 강철 드라이브: 2µs 미만의 DESAT 동작을 통해 단락 견고성이 향상되어 IGBT 시대의 보호 지연 및 관련 부수적 손상이 줄었습니다. 유지보수 호출은 여름 피크 부하 동안 눈에 띄게 감소했습니다.

선택 및 유지 관리 고려 사항

- 소자 페어링

- 드라이버 전류 및 전압 스윙을 모듈 게이트 전하 및 원하는 스위칭 속도에 맞추고, 켈빈 소스 가용성을 확인합니다.

- 면역 및 산화물 스트레스 한도의 균형을 맞추기 위해 음의 바이어스 레벨을 검증합니다.

- 보호 튜닝

- 모듈 특성 및 예상되는 스트레이 인덕턴스에 따라 DESAT 임계값 및 블랭킹 시간을 설정합니다.

- 에너지 소산을 연장하지 않으면서 VDS 오버슈트를 제한하기 위해 TLO 저항 크기를 구현합니다.

- PCB/레이아웃

- 루프 인덕턴스를 최소화하고, 전원 및 로직 접지를 분리하고, DESAT 및 감지 라인에 전용 리턴을 사용합니다.

- DC/DC 및 절연기를 높은 di/dt 노드에서 멀리 배치하고, MV 시스템에 적합한 크리피지/클리어런스를 적용합니다.

- 환경 강화

- 먼지에 대한 컨포멀 코팅을 적용하고, 고온 부품을 지정하고, 45~50°C 주변 온도에서 작동을 확인합니다.

- 검증

- dv/dt를 튜닝하기 위한 이중 펄스 테스트를 수행하고, TSC 반응을 검증하기 위한 단락 테스트를 수행하며, 전도/방사 방출에 대한 EMC 사전 적합성 테스트를 수행합니다.

산업 성공 요인 및 고객 사용후기

- 모듈 패키징 및 LCL 필터 팀과의 공동 설계를 통해 dv/dt 목표를 EMI 및 THD 목표에 맞춰 재설계 루프를 줄입니다.

- 초기 미션 프로파일 검증은 신뢰성을 유지하면서 과도한 엔지니어링 및 비용을 줄입니다.

고객 피드백:

"빠른 DESAT와 2단계 턴오프를 SiC 하프 브리지에 통합하여 드문 단락 이벤트로 인한 현장 고장을 제거했습니다. dv/dt 튜닝은 효율성을 저하시키지 않으면서 EMI 헤드룸을 개선했습니다." — 신드 지역 C&I PV 통합업체의 수석 전력 엔지니어

미래 혁신 및 시장 동향

- 실시간 전류 및 온도 감지를 기반으로 하는 적응형 dv/dt 제어를 갖춘 디지털 게이트 드라이버

- 게이트 전하 및 임계값 드리프트 추적을 위한 통합 상태 모니터링(SOH 메트릭)

- 다중 MW MV 시스템을 위한 더 높은 CMTI 절연 기술 및 더 낮은 공통 모드 커패시턴스

- 파키스탄의 MV PV 파이프라인(>5GW) 및 현지 제조 지원에 맞춰진 레퍼런스 설계

일반적인 질문 및 전문가 답변

- SiC MOSFET에 음의 게이트 바이어스를 사용하는 이유는 무엇입니까?

높은 dv/dt에서 밀러 커플링으로 인한 가짜 턴온을 방지하기 위해 사용합니다. 일반적인 값은 -3~-5V이며, 소자 한계 및 EMI 목표에 따라 선택됩니다. - DESAT 보호는 얼마나 빨라야 합니까?

고장 발생 시점부터 전류 차단까지 총 반응 시간을 ~2µs 미만으로 목표로 하고, 과전압 스트레스를 제한하기 위해 소프트 셧다운을 사용합니다. - 2단계 턴오프란 무엇이며 왜 사용합니까?

TLO는 고장 시 제어되고 더 부드러운 턴오프를 도입하여 VDS 오버슈트 및 스트레이 유도 링잉을 줄여 모듈과 게이트 산화물을 보호합니다. - 효율성을 잃지 않고 dv/dt를 튜닝하려면 어떻게 해야 합니까?

분할 Rg_on/Rg_off, 인덕턴스를 줄이는 레이아웃, 선택적으로 게이트 전류 성형을 사용하고, 이중 펄스 테스트를 통해 EMI와 스위칭 손실의 균형을 맞춥니다. - 이러한 드라이버는 먼지가 있는 45~50°C에서 안정적으로 작동할 수 있습니까?

예. 컨포멀 코팅, 디레이팅된 부품, 적절한 공기 흐름 또는 밀봉을 통해 드라이버는 안정성과 보호 성능을 유지합니다.

이 솔루션

이러한 SiC 중심 게이트 드라이버 회로는 파키스탄의 MV 상호 연결 및 고부하 산업용 드라이브에 필요한 제어 정밀도와 보호 속도를 제공합니다. 소형 LCL 필터에 더 높은 스위칭 주파수를 가능하게 하고, 덥고 먼지가 많은 환경에서 작동을 안정화하며, 손상 고장으로부터 보호하여 ≥98.5% 효율성, 최대 2배의 전력 밀도, 섬유, 시멘트, 강철 응용 분야에서 긴 수명을 제공합니다.

맞춤형 솔루션을 위해 전문가와 연결

전문 드라이버 설계 및 검증으로 SiC 전력 스테이지를 가속화하십시오.

- 10년 이상의 SiC 제조 전문 지식 및 응용 엔지니어링

- 절연, 보호 및 EMI 제어 분야의 혁신을 주도하는 선도적인 연구 생태계의 지원

- 열 및 기계적 신뢰성에 영향을 미치는 R-SiC, SSiC, RBSiC 및 SiSiC 구성 요소에 대한 맞춤형 제품 개발

- 현지 드라이버 조립 및 테스트를 위한 기술 이전 및 공장 설립 서비스

- 소자 및 드라이버에서 필터, 냉각, 규정 준수까지의 턴키 솔루션

- 효율성, 신뢰성 및 더 빠른 시장 출시를 제공하는 19개 이상의 기업에서 입증된 결과

무료 상담 및 맞춤형 게이트 드라이버 사양 패키지를 요청하십시오.

- 이메일: [email protected]

- 전화/왓츠앱: +86 133 6536 0038

MV PV 및 산업용 드라이브 출시와 일치하는 공동 설계, EMC 검증 및 현장 파일럿을 확보하기 위해 지금 2025~2026 개발 슬롯을 예약하십시오.

문서 메타데이터

최종 업데이트: 2025-09-10

다음 예정 업데이트: 2026-01-15

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.