1200V-3300Vデバイス製造と低欠陥密度を実現するカスタムドーピング・プロファイル付き大口径炭化ケイ素エピタキシャル・ウェーハ

シェア

製品概要と2025年の市場関連性

カスタムドーピングプロファイルと低欠陥密度基板で設計された大口径炭化ケイ素(SiC)エピタキシャルウェーハは、バッテリーエネルギー貯蔵システム(BESS)電力変換システム(PCS)、MVインバータ、および産業用ドライブで使用される高性能1200V〜3300Vデバイスの基盤です。パキスタンの繊維、セメント、 鉄鋼、および新たな産業部門では、11〜33kVフィーダーのグリッドの変動性、高い周囲温度(45〜50°C)、およびほこりが一般的であり、デバイスの品質はエピ層から始まります。正確なエピ厚さとドーピング制御を、超低欠陥率と組み合わせることで、導電損失とスイッチング損失の低減、より高い耐圧の一貫性、および歩留まりの向上に直接つながり、最終的に≥98%のPCS効率と1.8〜2.2倍の電力密度を実現します。

パキスタンの2025年のドライバー:

- C&Iおよびグリッド側のストレージの急速な成長(5年間で3〜5 GWh)は、グリッドコード要件(FRT、無効電力、低THD)を満たすために、高効率で信頼性の高いSiCデバイスを必要とします。

- ローカリゼーションの優先事項は、エピレシピを調整し、プロセスドキュメントを提供し、技術移転をサポートして、リードタイムを短縮し、国内の付加価値を高めることができるパートナーを支持します。

- 厳しい環境条件では、堅牢なリーク挙動、安定したしきい値電圧、および信頼性の高いエッジ終端を備えたデバイスが必要であり、これらはすべてエピ品質と均一性によって影響を受けます。

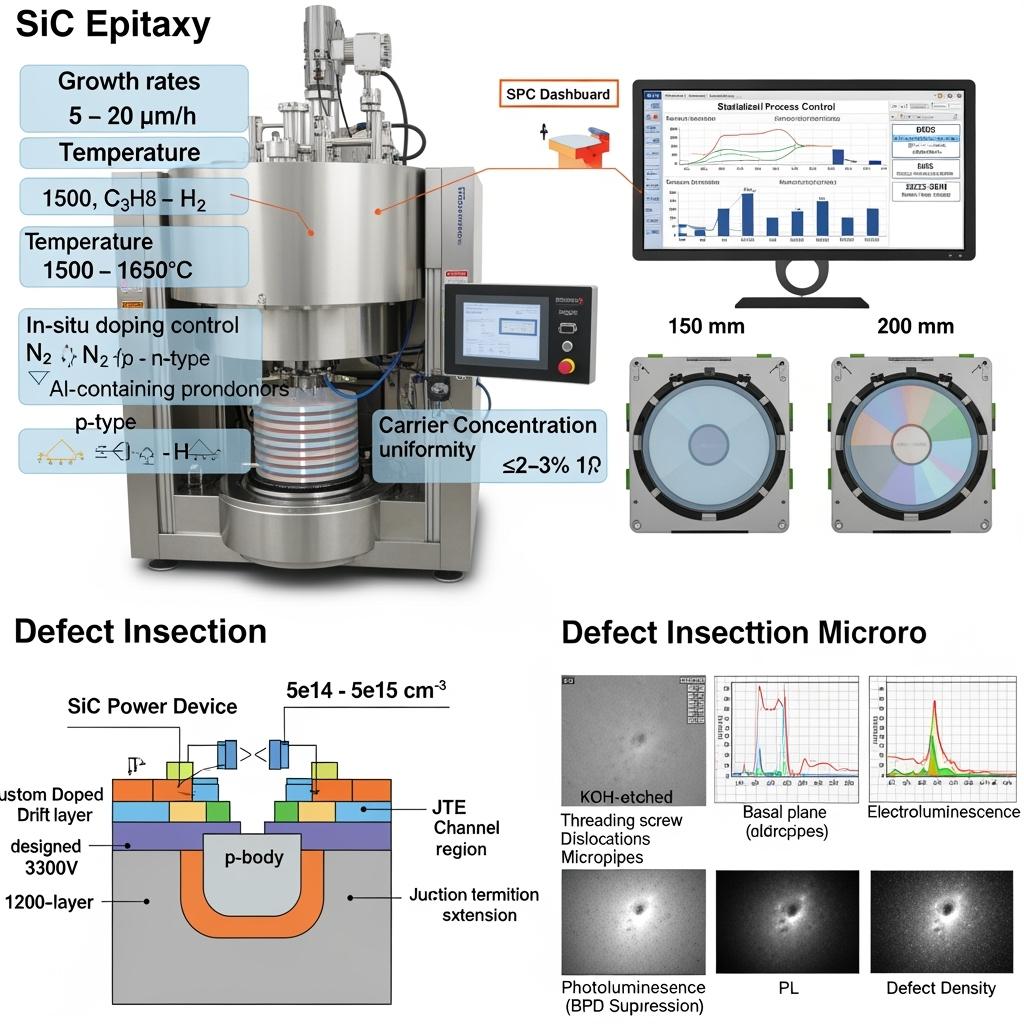

Sicarb Techは、MOSFET、ショットキーダイオード、JBSダイオード向けにカスタムエピスタックを備えた大口径ウェーハ(150 mm主流、200 mmロードマップ)を提供しており、エンジニアリングされたドリフト層、ボディ層、ジャンクション終端エクステンション(JTE)を含み、すべて1200V、1700V、2200V、3300Vデバイス製造向けに認定されています。

技術仕様と高度な機能

- ウェーハ径と基板

- 150 mm標準、200 mmロードマップ互換性

- 低マイクロパイプ基板、スレッドスクリュー転位(TSD)および基底面転位(BPD)抑制プロセス

- エピタキシャル層

- ドリフト層厚さ:5~100 µm(電圧クラス別の代表的な範囲)、ウェーハ全体で均一性±2~3%

- ドーピング濃度:5e14~5e16 cm^-3(カスタムプロファイル)、±10%の目標許容範囲またはそれ以上

- 多層スタック:JTEエピ層、チャネルエンジニアリング、ゲート酸化膜完全性のためのエピレディ表面

- ドーピングと界面品質

- 窒素によるn型ドーピング、制御されたメモリ効果を持つアルミニウム前駆体によるp型ドーピング

- チャネル移動度と安定した閾値電圧(Vth)を改善するための低トラップ密度

- 表面形態:ゲート酸化膜とイオン注入ステップ用にRMS粗さを最適化

- 欠陥制御と計測

- インライン厚さおよびキャリアマッピング、プロファイルのSIMS検証

- BPD/TSD評価のためのKOHエッチング、エピ均一性と欠陥局在化のためのPL/EL

- 試験構造によるリークおよび破壊の事前スクリーニング、統計的サンプリング

- プロセス統合の準備

- 1200V~3300V MOSFET、JBSダイオード、ショットキーダイオード向けに調整されたレシピ

- イオン注入/アニールアライメントおよびJTE設計用のドキュメントパッケージ

- クリーンルームハンドリング:FOUP/SMIF、ISO 5~7互換ワークフロー

比較の視点:高電圧SiCデバイス用のカスタム低欠陥エピ対コモディティエピ

| 基準 | カスタム低欠陥SiCエピ(150/200 mm、調整されたプロファイル) | コモディティエピ(一般的なプロファイル) |

|---|---|---|

| ブレークダウン電圧の一貫性 | 精密なドリフト/JTE制御による厳しいBV分布 | より広いBVスプレッド、より多くのビニングとフォールアウト |

| 導通/スイッチング損失 | 面積あたりのRDS(on)が低い、安定したリーク | 損失が高い、リーク変動が増加 |

| 歩留まりとテストスループット | より高いダイ歩留まり、エッジ終端不良が少ない | 歩留まりが低い、テストとリワークサイクルが長い |

| 厳しい環境での信頼性 | より優れたリーク安定性とVthドリフト制御 | ドリフトリスクの上昇、初期故障 |

| 位置情報とリードタイム | レシピ転送とローカルサポートオプション | カスタマイズの制限、より長いサプライチェーン |

専門家による引用による主な利点と実証済みのメリット

- システムレベルでの性能向上:デバイス損失の低減とBVの厳格化により、≥98%のPCS効率と磁気部品/冷却サイズの削減が可能になり、キャビネット容積が30%以上向上します。

- 歩留まりとコスト:低欠陥エピは、テストフォールアウトを削減し、必要な電圧クラスでのウェーハあたりのダイ数を増やし、生産スケジュールを安定させます。

- パキスタンの状況における信頼性:エピ品質は、リークドリフト、ゲート酸化膜界面安定性、およびJTEの堅牢性に直接影響します。これは、45~50°Cの周囲温度と埃っぽい環境にとって不可欠です。

専門家の視点

“High-voltage SiC device performance is highly sensitive to epitaxial layer quality—thickness and doping uniformity, low defect densities, and engineered terminations are crucial for yield and reliability.” — IEEE Transactions on Electron Devices, SiC epitaxy and high-voltage device design (https://ieeexplore.ieee.org)

実際のアプリケーションと測定可能な成功事例

- 100~250 kW PCS用の1200V MOSFETプラットフォーム:最適化された表面形態を持つカスタムドリフト層(10~12 µm、〜1e16 cm^-3)により、デバイスRDS(on)が〜8~10%削減され、パンジャブC&Iストレージにおける〜100 kHzスイッチングで0.5~0.7%のPCS効率向上に貢献しました。

- PFCおよびフリーホイール用の1700V JBSダイオード:低BPD密度と調整されたJTE層を備えたエピにより、150°Cでの逆リークが〜30~40%削減され、より小型のヒートシンクが可能になり、シンド州の繊維工場での稼働時間が向上しました。

- MVインバータ用の3300Vパイロット:精密なキャリア濃度グレーディングを備えた多層エピにより、BV分布の厳格性が50%以上向上し、テストフォールアウトが削減され、パキスタン南部でのグリッド側認証が迅速化されました。

選択とメンテナンスの考慮事項

- 電圧クラスとミッションプロファイル

- パキスタンの産業用デューティサイクルに典型的なターゲットBV(1200/1700/2200/3300V)および熱ミッションプロファイルに合わせて、ドリフト厚さとドーピングを調整します。

- 欠陥目標

- 最大許容BPD/TSD密度を指定し、基板およびエピサプライヤがKOH/PLメトリックとロットトレーサビリティを提供することを確認します。

- インターフェースとプロセス結合

- 界面品質とVth安定性を維持するために、ゲート酸化膜成長、イオン注入、および高温活性化(最大1700~2000°C)とエピ表面処理を調整します。

- JTEとエッジ終端

- エピアシストJTE層を使用してBVを厳格化し、エッジリークを削減します。フルウェーハ実行の前に、TCADと試験構造で検証します。

- サプライチェーンとEHS

- FOUP/SMIFハンドリング、安定したロジスティクス、およびMES統合を確保します。ユーティリティプロジェクトのタイムラインに対応するために、ローカル在庫バッファを計画します。

業界の成功要因と顧客の声

- エピタキシー、イオン注入/アニール、および終端レイアウト全体での共同最適化により、最高のデバイス性能と信頼性が得られます。

- 厳格なSPCとインライン計測により、ロット間のばらつきを最小限に抑え、下流のパッケージングとシステム検証を安定させます。

お客様の声:

「カスタムエピプロファイルは、破壊分布を厳格化し、リークを削減しました。これにより、PCS効率が向上し、グリッドコンプライアンスがスムーズになりました。」—パキスタンを拠点とするパワーエレクトロニクスOEMのデバイスエンジニアリングディレクター

将来のイノベーションと市場トレンド

- 改善されたリアクタスループットと均一性制御を備えた200 mm SiCウェーハへの移行

- よりシャープなプロファイルとメモリ効果の低減のための高度なドーピング技術とインシチュモニタリング

- 高電圧クラスでのBVをさらに厳格化するためのエピ対応電界プレートと終端構造

- ローカライゼーションパス:パキスタンでのエピ仕上げ、ウェーハテスト、およびモジュールアセンブリを確立するための合弁事業

よくある質問と専門家による回答

- 1700V MOSFETにはどのようなエピ厚さとドーピングが必要ですか?

典型的なドリフト層は、ドーピングが1e16 cm^-3台の約12~15 µmです。正確な値は、デバイスアーキテクチャと、必要なRDS(on)/BVのトレードオフによって異なります。 - BPDのような欠陥は、デバイスにどのように影響しますか?

BPDは、ダイオードの順方向電圧ドリフトを促進し、リークに影響を与える可能性があります。低欠陥エピは、信頼性を向上させ、パラメータドリフトを削減します。 - カスタムエピは、LCLフィルタサイズの削減に役立ちますか?

間接的に、はい。より高いスイッチング周波数でのデバイス損失の低減により、ゲートドライブと制御の共同設計を条件として、より小型の磁気部品とフィルタが可能になります。 - 150/200 mmウェーハ全体でドーピングの均一性をどのように確保していますか?

リアクタフローの最適化、サセプタ設計、インシチュモニタリングを通じて、成長後のマッピングとSPCにより、均一性を±2~3%(厚さ)以内に保ち、キャリアを厳密に制御します。 - エピ層は高温活性化と互換性がありますか?

はい。エピ表面とドーピングプロファイルは、界面の完全性を維持するために、適切なキャッピングとクリーンアップを使用して、1700~2000°Cのアニールに耐えるように設計されています。

このソリューションがお客様の業務に役立つ理由

パキスタンの産業用PCSおよびMVインバータプログラムの場合、デバイスの卓越性はエピタキシーから始まります。大径、低欠陥SiCエピとカスタムドーピングにより、以下が可能になります。

- ≥98%の効率のための、より低い導通/スイッチング損失

- より高い歩留まりとより迅速な認証のための、より厳格なBVとリーク分布

- 45~50°Cの埃っぽい環境での安定した動作により、長いMTBFとメンテナンスの削減をサポート

この基盤は、下流の製造、パッケージング、およびシステム試運転のリスクを軽減し、ROIと市場投入までの時間を加速します。

カスタムソリューションについては専門家にご相談ください

デバイスロードマップを満たすエピを指定および提供するために、Sicarb Techと提携してください。

- 材料、エピ、およびデバイス全体にわたる10年以上のSiC製造専門知識

- 継続的なイノベーションと計測のための中国科学院の支援

- R-SiC、SSiC、RBSiC、SiSiCコンポーネントおよび高度なエピスタック全体でのカスタム開発

- パキスタンでのローカル能力のための技術移転および工場設立サービス

- エピタキシーとイオン注入/アニールからデバイステスト、モジュールパッケージング、コンプライアンスまでのターンキーソリューション

- より高い効率、歩留まり、および市場投入までの時間を達成した19以上の企業との実績

エピ仕様、欠陥目標、およびプロセス統合計画について、無料相談をリクエストしてください。

- Eメール:[email protected]

- 電話/WhatsApp:+86 133 6536 0038

パキスタンの急速に成長するPCSおよびMVインバータ需要に対応するために、SiCデバイス生産を拡大するための2025~2026ウェーハ割り当てとレシピ転送スロットを確保してください。

記事のメタデータ

最終更新日:2025年9月10日

次回の予定更新日:2026年1月15日

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.