裏面メタライゼーション対応と低チップダイシングのための一体型炭化ケイ素ウェハ切断・薄片化装置

シェア

製品概要と2025年の市場関連性

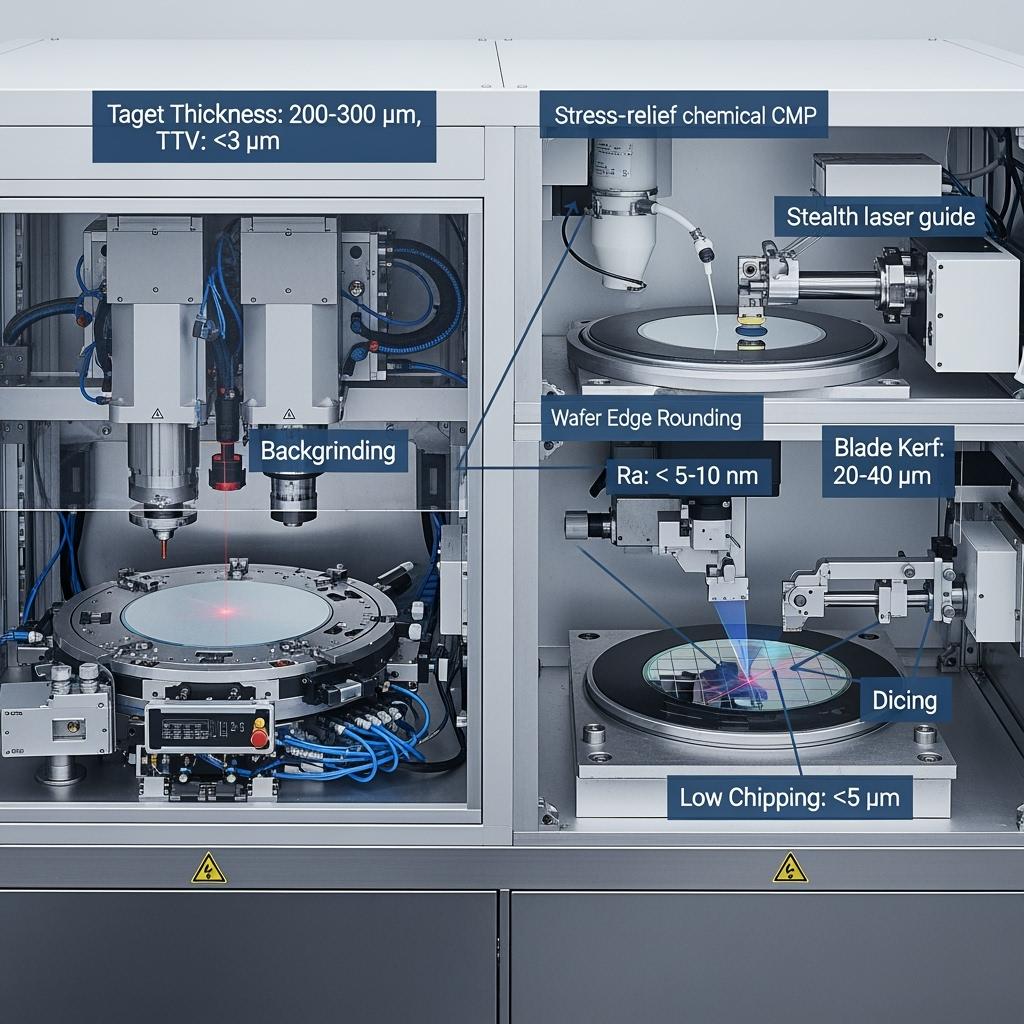

炭化ケイ素(SiC)用に特別に設計された統合ウェーハ切断および薄型化マシンは、精密なバックエンドオブライン(BEOL)準備を可能にします—バックグラインディング、応力緩和、研磨、および低チップダイシング—これにより、ウェーハは裏面金属化、薄型化依存デバイス性能、および高歩留まりダイシングの準備が整います。バッテリーエネルギー貯蔵システム(BESS)PCS、MVインバータ、および産業用ドライブを供給するパキスタンの加速するパワーエレクトロニクスエコシステムにとって、これらのツールは市場投入までの時間を短縮し、デバイス歩留まりを向上させ、ローカリゼーションの目標をサポートします。

SiCの硬度と脆性(Mohs〜9.5)により、機械加工が困難になります。不適切な薄型化とダイシングは、耐圧を低下させ、リークを増加させ、モジュールの信頼性を低下させるマイクロクラックとチッピングを誘発します—特に、パキスタンの繊維、セメント、および 鉄鋼 施設で一般的な45〜50℃の周囲温度、埃、および振動の下で。適応型研削/研磨、応力緩和化学薬品、ステルス/レーザースクライブ、およびブレードまたはハイブリッドダイシングを備えた統合ラインは、エッジの完全性を高く保ち、粒子汚染を低く抑え、Ag焼結アタッチおよび高熱伝導率セラミック基板(Si3N4/AlN)に適合したダイを提供します。

2025年、パキスタンが3〜5GWhの新しいエネルギー貯蔵とより深い産業電化をターゲットにしているため、SiCウェーハ準備とシングレーションへのローカルアクセスは、供給の回復力を高め、輸入リードタイムを短縮し、技術移転イニシアチブと連携し、PCS効率、電力密度、およびMTBFに直接影響を与えます。

技術仕様と高度な機能

- 薄型化と平坦度

- バックグラインド厚さ範囲:150/200mmウェーハの場合、通常150〜350µmまで。超薄型ターゲット用の高度なキャリア

- 全厚さ変動(TTV):≤±3〜5µm(研磨後)。温度安定化チャックによるウェーハの反り/ワープ制御

- 表面粗さ:ポストCMP/研磨Ra≤5〜10nmで、裏面金属の接着と熱接触を最適化

- エッジの完全性と損傷制御

- 応力緩和プロセス:微研削+サブサーフェスダメージ(SSD)を除去するための独自のスラリーを使用したCMP

- ダイシング中のクラック発生を抑制し、モジュールアセンブリを行うためのエッジ丸めと面取り研磨

- ダイシングの柔軟性

- 表面損傷を軽減するためのステルスレーザースクライビング(赤外線)、次にブレードまたはステルスのみの分離

- 超薄型ブレード(20〜40µmケルプ)、最適化された送り速度、およびクーラント供給を備えたブレードダイシング

- 典型的なチッピング:上/下エッジで≤3〜5µm。アクティブウォッシュ/乾燥による低粒子発生

- メトロロジーとSPC

- インライン厚さ、TTV、および反りマッピング。光学エッジ検査。自動画像分析によるチッピング測定

- 裏面金属接着要件と互換性のある粒子カウンターとダイシング後の清浄度チェック

- 自動化と汚染制御

- FOUP/SMIFハンドリング。ISO 5〜7クリーンゾーン。HEPAダウンフロー。DI水回収とろ過

- SECS/GEM、OPC-UA接続。レシピ/バージョン管理とロット系譜

- 安全性とEHS

- レーザークラス安全インターロック。クーラント/化学物質の監視。非常停止。人間工学に基づいたメンテナンスアクセス

比較概要:統合SiC薄型化/ダイシング対従来のシリコンライン

| 基準 | 統合SiCウェーハ切断および薄型化マシン | 従来のシリコンに焦点を当てたツール |

|---|---|---|

| SiCのエッジチッピング | ステルス+最適化されたブレードで≤3〜5µm | 通常は>10µm。クラックのリスクが高い |

| サブサーフェスダメージの除去 | 専用SiC応力緩和およびCMP | 限定的。より高いSSDが残っています |

| TTVと反り制御 | 温度安定化チャックによる厳密な制御 | 硬くて脆いSiCには効果が低い |

| 裏面金属化の準備 | Ra≤5〜10nm。クリーンな表面化学 | 追加のリワークが必要になることがよくあります |

| 歩留まりと信頼性への影響 | より高いダイ歩留まり。より良いBVとリーク | 故障と現場リスクの増加 |

専門家による引用による主な利点と実証済みのメリット

- より高いデバイス

- 背面金属プロセス準備:制御された粗さとクリーンな

- ローカライゼーションとスピード:国内でのウェーハ準備は、ロジスティクスのリスクを削減し、迅速なエンジニアリングターンをサポートし、パキスタンの産業高度化目標に合致します。

専門家の視点

“SiC’s mechanical hardness and brittleness demand specialized thinning and dicing strategies; controlling sub-surface damage and edge chipping is critical for high-voltage device yield and reliability.” — IEEE Transactions on Electron Devices, SiC back-end processing insights (https://ieeexplore.ieee.org)

実際のアプリケーションと測定可能な成功事例

- 1200 Vデバイス向け150 mm MOSFETライン:ステルススクライブ+ブレードダイシングへの移行により、最適化されたCMPにより、平均エッジチッピングが約9 µmから約3 µmに減少し、リーク関連のテストフォールアウトが約35%減少しました。パンジャブ州でのPCS展開における下流の効率は、より厳しいデバイス分布により、約0.4〜0.6%向上しました。

- 産業用ドライブ向け1700 V JBSダイオード:TTVが±3 µmに締め付けられ、裏面Ra〜7 nmにより裏面金属の密着性が向上し、シンド州の繊維工場全体でリーク関連の故障によるフィールドリターン率が30%以上低下しました。

- 200 mmパイロットの準備完了:200 mmキャリアおよびチャック冷却用に統合されたラインを改造し、ボウ/ワープを安定化させ、MVインバータデバイスの初期ウェーハデモを可能にし、一貫したBV均一性と約45%のビン分布の削減を実現しました。

選択とメンテナンスの考慮事項

- プロセスレシピ設計

- SSDを最小限に抑えるために、CMPの前に多段階研削(粗→微細)を選択し、該当する場合は断面およびマイクロラマン/PLで検証します。

- ブレードタイプ、送り速度、および冷却剤の化学組成を設定します。ステルスを使用する場合は、ストリート幅とウェーハの厚さに対するスクライブ深さを最適化します。

- メトロロジーとSPC

- TTV、Ra、チッピングヒストグラム、およびパーティクルカウントをロットごとに追跡し、自動アラーム付きの制御限界を展開します。

- 高解像度光学系を介してエッジを検査し、フィードバックのためにチッピングをデバイスのリーク/BV分布と相関させます。

- 消耗品管理

- ブレード寿命ログ、スラリーろ過、およびDI水質を維持します。レーザー、光学系、およびチャックのスペアを計画します。

- 清潔さと安全性

- 堅牢なダイシング後のクリーン/乾燥を確保します。裏面メタライゼーションまたは焼結を損なう可能性のある残留物を監視します。

- レーザー安全および化学物質取り扱いSOPを遵守します。オペレーターのトレーニングを提供します。

- アップストリーム/ダウンストリームとの統合

- エピタキシーフラットの方向、インプラント/アニール計画、および裏面金属スタックに合わせます。キャリアの互換性とワープ仕様を確保します。

業界の成功要因と顧客の声

- デバイス、プロセス、およびパッケージングチーム間の緊密な連携が不可欠です。エッジの完全性とTTVは、Ag焼結アタッチの歩留まりとモジュールの熱抵抗に直接影響します。

- データ駆動型のフィードバックループ(SPCから電気的テストKPI)は、手直しを削減し、スケジュールを安定させます。

お客様の声:

「統合されたSiC薄化およびステルスダイシングラインにより、リークフォールアウトが半減し、裏面金属の密着性が一貫しました。当社のPCSモジュールは、最初の実行で熱およびグリッドテストに合格しました。」—パキスタンを拠点とするデバイスファブパートナーの運用マネージャー

将来のイノベーションと市場トレンド

- 先進的な研削ホイール、改良されたチャック冷却、およびAI駆動のレシピ調整による200 mm SiCの準備

- マイクロクラックをさらに抑制するためのハイブリッドレーザー技術(超高速フェムト秒)

- 100%検査のためのIR/超音波によるインラインエッジクラック検出

- パキスタンでのローカライゼーション:設備資金調達、労働力トレーニング、およびMES統合によるウェーハ準備セルの設立のための合弁事業

よくある質問と専門家による回答

- SiCにステルススクライブ+ブレードが好まれるのはなぜですか?

ステルスは、ダイシングストリートに沿ってウェーハを事前に弱化させ、ブレード分離中の機械的応力を低減し、チッピングを3〜5 µm以下に抑えます。 - 裏面メタライゼーションに許容されるTTVはどれくらいですか?

ほとんどの1200〜1700 Vデバイスの場合、TTV≤±3〜5 µmを目標とし、均一な金属厚さ、パッケージングの良好な平面性、および予測可能な熱経路を確保します。 - 薄化は信頼性にどのように影響しますか?

低SSD薄化は、熱サイクル下で伝播する可能性のあるマイクロクラックを減らし、特に高温環境下でのBV安定性とリークを改善します。 - 既存のシリコンダイシングツールはSiCを処理できますか?

信頼できません。SiCは、低チップ結果を達成するために、調整されたブレード、冷却剤供給、チャック温度制御、および多くの場合、ステルス/レーザー支援を必要とします。 - 裏面金属の前に必要な清浄度はどれくらいですか?

低いパーティクルカウント、最小限の残留物、および5〜10 nmのRaが一般的です。ダイシング後のクリーンおよび表面活性化ステップが推奨されます。

このソリューションがお客様の業務に役立つ理由

パキスタンのSiCデバイスロードマップでは、堅牢なウェーハ薄化と低チップダイシングは不可欠です。統合されたマシンは、裏面メタライゼーションの準備、厳しいTTV、および完全なエッジを提供し、リークとBV分布を減らし、ダイの歩留まりを向上させ、信頼性の高いAg焼結モジュールアセンブリを可能にします。その対価は、より迅速な認証、より高いPCS効率(≥98%)、コンパクトなパッケージング、および45〜50°Cのほこりの多い産業環境での長いフィールド寿命です。

カスタムソリューションについては専門家にご相談ください

Sicarb TechでSiCバックエンドをスケールアップ:

- 10年以上のSiC製造専門知識

- プロセスと計測の革新に対する中国科学院の支援

- R-SiC、SSiC、RBSiC、SiSiC材料および完全なエピタキシーからモジュールへのフロー全体にわたるカスタム開発

- パキスタン向けの技術移転および工場設立サービス(設備仕様、SOP、トレーニング、SAT/FAT、MES統合を含む)

- エピタキシーとインプラントからウェーハ準備、裏面金属、デバイステスト、およびモジュールパッケージングまでのターンキーソリューション

- より高い歩留まり、より厳しいBV、およびより速い市場投入を実現する19以上の企業の実績

薄化/ダイシングレシピ、計測計画、およびローカライゼーションロードマップに関する無料相談をリクエストしてください:

- Eメール:[email protected]

- 電話/WhatsApp:+86 133 6536 0038

2025〜2026年の設備スロットとプロセス転送ウィンドウを確保し、スケールアップのリスクを軽減し、パキスタンの成長するPCSおよびMVインバータの機会を捉えます。

記事のメタデータ

最終更新日:2025年9月10日

次回の予定更新日:2026年1月15日

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.