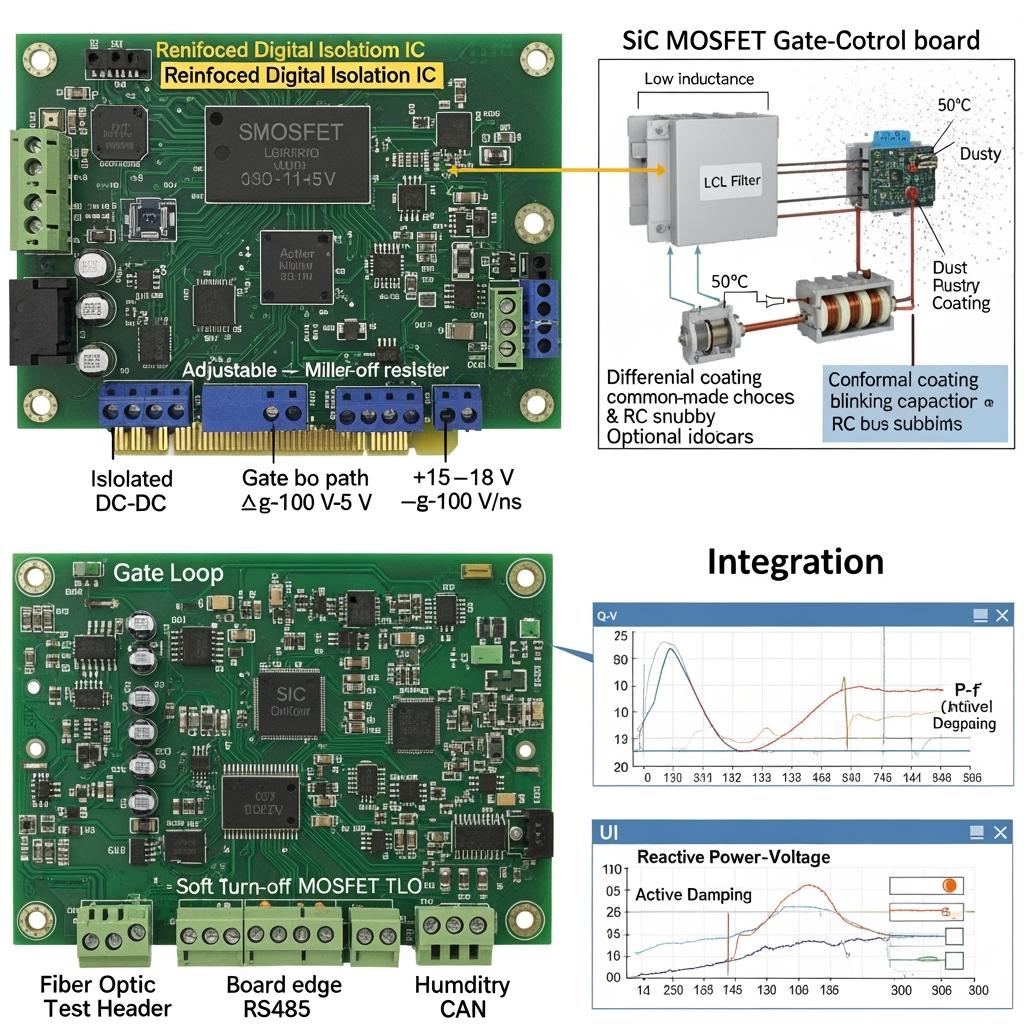

アクティブ・ミラークランプ、負バイアス、50~200kHz動作の高CMTI絶縁を備えた炭化ケイ素MOSFETゲートドライブ・コントロール・ボード

シェア

製品概要と2025年の市場関連性

炭化ケイ素(SiC)MOSFETゲートドライブ制御ボードは、バッテリエネルギー貯蔵システム(BESS)電力変換システム(PCS)およびMVインバータにおける高周波、高効率動作を解き放つための要です。パキスタンの繊維、セメント、 鉄鋼、および新興産業部門では、コンバータは、不安定な11~33 kVフィーダで≥98%の効率、コンパクトなフットプリント、および安定した動作を実現する必要があります。これらはすべて、産業団地で一般的な45~50°Cの周囲温度と埃っぽい環境に耐えながら行われます。

専用のSiCゲートドライブボードは、以下を組み合わせることにより、50~200 kHzでの正確で再現性のあるスイッチングを可能にします。

- 誤トリップなしで高速dv/dtエッジを許容するための高CMTI強化絶縁

- 寄生ターンオンを抑制するためのアクティブミラークランプと構成可能な負ゲートバイアス

- 高速で制御された障害処理のための2レベルターンオフ(TLO)を備えたDESAT保護

- 対称ハーフブリッジスイッチングのための厳密な伝搬遅延マッチング

- LCLアクティブダンピング、グリッド追従(GFL)およびグリッド形成(GFM)モード、Q–VおよびP–fドロップ、およびFRT動作のためにPCS制御と連携するインターフェース

これらの機能は、より小型の磁気部品とフィルタ、弱いフィーダでのより短い試運転、不要なトリップの削減、および過酷な条件下での稼働時間の向上という測定可能なメリットをもたらします。パキスタンが3~5 GWhのC&Iおよびグリッド側ストレージを追加する2025年の展開では、SiC最適化ゲートドライブボードがプログラムのリスクを軽減し、ROIを加速します。

技術仕様と高度な機能

- 電気的および絶縁

- ゲート電圧レール:+15~+18 Vターンオン、-3~-5 Vターンオフ(構成可能なモジュール)

- ピークドライブ電流:管理されたEMIによる鮮明なエッジのための8~30 Aクラス

- 絶縁強度:関連するIEC/ULに適合する強化絶縁、50~200 kHzスイッチング用のCMTI≥100 V/ns

- 伝搬遅延とスキュー:≤100 nsの総伝搬、≤30~50 nsのチャネル間スキュー

- 保護と障害処理

- プログラマブルブランキング(例:200~800 ns)とソフト2レベルターンオフによるDESAT保護により、過電圧を制限

- 正と負の両方のレールでのUVLO/OVLO、デバイスCgdに調整されたミラークランプ活性化しきい値

- プログラマブル障害ラッチング、障害カウンタ、およびタイムスタンプ付きログ

- dv/dt制御とEMI

- 独立したターンオン/オフRg、微調整用のオプションのスプリットゲート抵抗フットプリント

- 誘導結合を低減するためのケルビンソースピンルーティングとスターグラウンドトポロジー

- ファームウェアを介してロードされたオプションのRCスナバとdV/dtスルー制御プロファイル

- 制御調整とインターフェース

- PLL、GFL/GFM、Q–V、P–fドロップ、アクティブLCLダンピング、およびFRTカーブを実装するメイン制御ボードへのデジタルリンク

- テレメトリ:ゲート電圧、DESATイベント、温度センサー、ノイズの多い環境用のオプションのファイバ絶縁

- 環境的堅牢性

- 動作周囲温度:-40°C~+105°C、高湿度定格のコンポーネント、コンフォーマルコーティングオプション

- I/OのESD/サージ保護、クリープ/クリアランスを維持するためのコーティングクリアランス

性能比較:SiC最適化ゲートドライブ対従来のIGBT指向ドライバ

| 基準 | SiC MOSFETゲートドライブ制御ボード(50~200 kHz最適化) | 従来のIGBT指向ゲートドライバ |

|---|---|---|

| スイッチング周波数能力 | 50~200 kHz(dv/dt制御あり) | 5~20 kHzが一般的、より高いfswでは制限あり |

| dv/dtイミュニティ(CMTI) | ≥100 V/ns強化絶縁 | より低いCMTI、より高い誤トリップリスク |

| 故障保護 | DESAT + TLO、高速かつ制御可能 | 低速OCP; より高いオーバーシュート/ストレス |

| EMIおよびTHDへの影響 | クリーンなエッジ、より小型のLCLフィルタ | より大きなフィルタ; EMIの増加 |

| 弱電網での試運転 | 協調的なアクティブダンピングとグリッドモード | より長いチューニング; 不安定性のリスク |

専門家による引用による主な利点と実証済みのメリット

- より高い効率と密度: 安定した高周波スイッチングは、コンパクトなLCLフィルタと磁気部品をサポートし、98%以上のPCS効率と30%以上の体積削減を実現します。

- 堅牢な保護と稼働時間: 制御されたTLOを備えたDESATは、故障エネルギーとオーバーシュートを制限し、高価なSiCモジュールを保護し、トリップを最小限に抑えます。

- より高速な相互接続コンプライアンス: ドロップ制御、FRT、アクティブダンピングとの連携により、MVグリッドの受け入れを加速します。

専門家の視点

“Gate drivers for wide bandgap transistors must provide fast, deterministic protection and finely controlled slew rates to realize efficiency advantages without compromising reliability.” — IEEE Transactions on Power Electronics, WBG gate-driver design guidance (https://ieeexplore.ieee.org)

実際のアプリケーションと測定可能な成功事例

- パンジャブ2 MW/4 MWh PCS: DESAT/TLOおよびアクティブダンピングプリセットを備えたSiCドライバは、約100 kHzの動作を可能にし、システム効率を98.2%に向上させ、キャビネットの体積を35%削減し、弱いフィーダー状態にもかかわらず、試運転を約30%短縮しました。

- シンドの繊維工場のドライブ: 負のバイアスとミラークランプにより、寄生的なターンオンが排除され、50℃の夏の間におけるEMIトリップが削減されました。稼働時間が改善され、メンテナンス間隔が延長されました。

- パキスタン南部におけるMVインバータのパイロット: GFM連携により、電圧降下中の電圧が安定化し、無効電力サポート(Q–V)により電力品質目標が達成され、最初のユーティリティ承認が得られました。

選択とメンテナンスの考慮事項

- デバイスの互換性とサイジング

- ドライバのピーク電流をモジュールのゲート電荷(Qg)および必要なdv/dtに合わせ、ケルビンソースピンが利用可能であることを確認します。

- PCBレイアウトと寄生要素

- ゲートループ領域を最小限に抑え、リターンパスに密接に結合し、高dv/dtノードをロジックトレースから分離します。

- 保護調整

- データシートSOAからDESATしきい値を設定し、実際の故障を捕捉しながらノイズトリガを回避するようにブランキングを調整し、2レベルターンオフタイミングを確認します。

- 環境の強化

- コンフォーマルコーティングを適用し、耐食性仕上げを選択し、冷却エンクロージャの防塵フィルタメンテナンスを計画します。

- 検証ワークフロー

- ダブルパルス試験を実行してRgとスルーを調整し、DESAT/TLOの動作を相関させ、フルパワー試験の前にHIL試験でアクティブダンピングとドロップの相互作用をテストします。

業界の成功要因と顧客の声

- ゲートドライブ、パワーレイアウト、LCLフィルタ、制御ファームウェアをリンクするチーム間の共同設計は、高周波安定性と低THDに不可欠です。

- パキスタンのユーティリティとフィーダーの強度に合わせて調整されたパラメータパックは、フィールドロールアウトを加速します。

お客様の声:

「SiC固有のゲートドライバは、迷惑なトリップをなくし、EMIペナルティなしでスイッチング周波数を上げることができました。グリッドテストは簡単でした。」—パキスタンESSインテグレータの主任電力エンジニア

将来のイノベーションと市場トレンド

- 予測メンテナンスのためのゲートドライバ内蔵の接合温度推定と電流センシング

- グリッドイベントに対応して損失と安定性のバランスを取る適応型スルーレート変調

- ユーティリティが立ち会うテスト用の署名付きパラメータパックによる安全な無線(OTA)アップデート

- リードタイムを短縮し、サービスを強化するためのパキスタンにおけるドライバアセンブリとテストのローカライズ

よくある質問と専門家による回答

- SiC MOSFETに負のゲートバイアスは必要ですか?

はい、通常-3~-5 Vは、高dv/dt遷移中、特にハーフブリッジレッグでミラー容量を介した寄生ターンオンを防ぐのに役立ちます。 - どのCMTI定格を目標とすべきですか?

50~200 kHzのスイッチングで誤トリガを回避するために、強化絶縁を備えた100 V/ns以上のCMTIを目指してください。 - 2レベルターンオフはどのようにして故障ストレスを軽減しますか?

TLOは、DESAT検出後に制御された、より遅いターンオフパスを挿入し、VDSオーバーシュートとdi/dtを制限して、デバイスとモジュールを保護します。 - これらのドライバは、弱電網の試運転に役立ちますか?

はい。アクティブダンピングとドロップ制御との連携により、電圧降下/上昇中の電流と電圧が安定し、ユーティリティの承認が容易になります。 - Rg値を調整するには?

ダブルパルス試験を使用して、スイッチング損失とEMIのバランスを取ります。個別のターンオン/オフ抵抗を使用し、必要に応じて、より細かい制御のためにスプリットゲートパスを使用します。

このソリューションがお客様の業務に役立つ理由

パキスタンの産業環境は高温、多湿、グリッドに課題があります。アクティブミラークランプ、負バイアス、高CMTI絶縁、DESAT/TLO保護を備えたSiC MOSFETゲートドライブ制御ボードは、SiCのデバイスの利点をフィールド結果に変換します。つまり、98%以上の効率、コンパクトなフットプリント、トリップの削減、迅速なグリッドコンプライアンスです。その結果、稼働時間の増加、LCOEの削減、繊維、セメント、鉄鋼、および新興セクター全体でのより速いペイバックが実現します。

カスタムソリューションについては専門家にご相談ください

SiCゲートドライブプラットフォームの設計、検証、およびスケーリングについては、Sicarb Techと提携してください。

- 10年以上のSiC製造およびアプリケーションエンジニアリングの専門知識

- デバイス、パッケージング、および制御イノベーションについては、中国科学院の支援を受けています。

- R-SiC、SSiC、RBSiC、SiSiC材料および高度なゲートドライブ/制御スタック全体にわたるカスタム開発

- パキスタンでの生産とテストをローカライズするための技術移転と工場設立サービス

- 材料とデバイスからゲートドライブ、モジュール、LCLフィルタ、冷却、コンプライアンスドキュメントまでのターンキーソリューション

- より高い効率、より速い試運転、および信頼性の高い動作を達成した19以上の企業による実績

ドライバ仕様、保護調整、および試運転パラメータパックについては、無料相談をリクエストしてください。

- Eメール:[email protected]

- 電話/WhatsApp:+86 133 6536 0038

2025~2026年の共同設計および検証スロットを確保し、グリッドコードコンプライアンスを加速し、EMIリスクを軽減し、パキスタンの産業ハブ全体での展開を拡大しましょう。

記事のメタデータ

最終更新日:2025年9月10日

次回の予定更新日:2026年1月15日

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.