dv/dt制御、短絡保護、DESATセンシングを備えた炭化ケイ素MOSFETゲート・ドライバ回路

シェア

製品概要と2025年の市場関連性

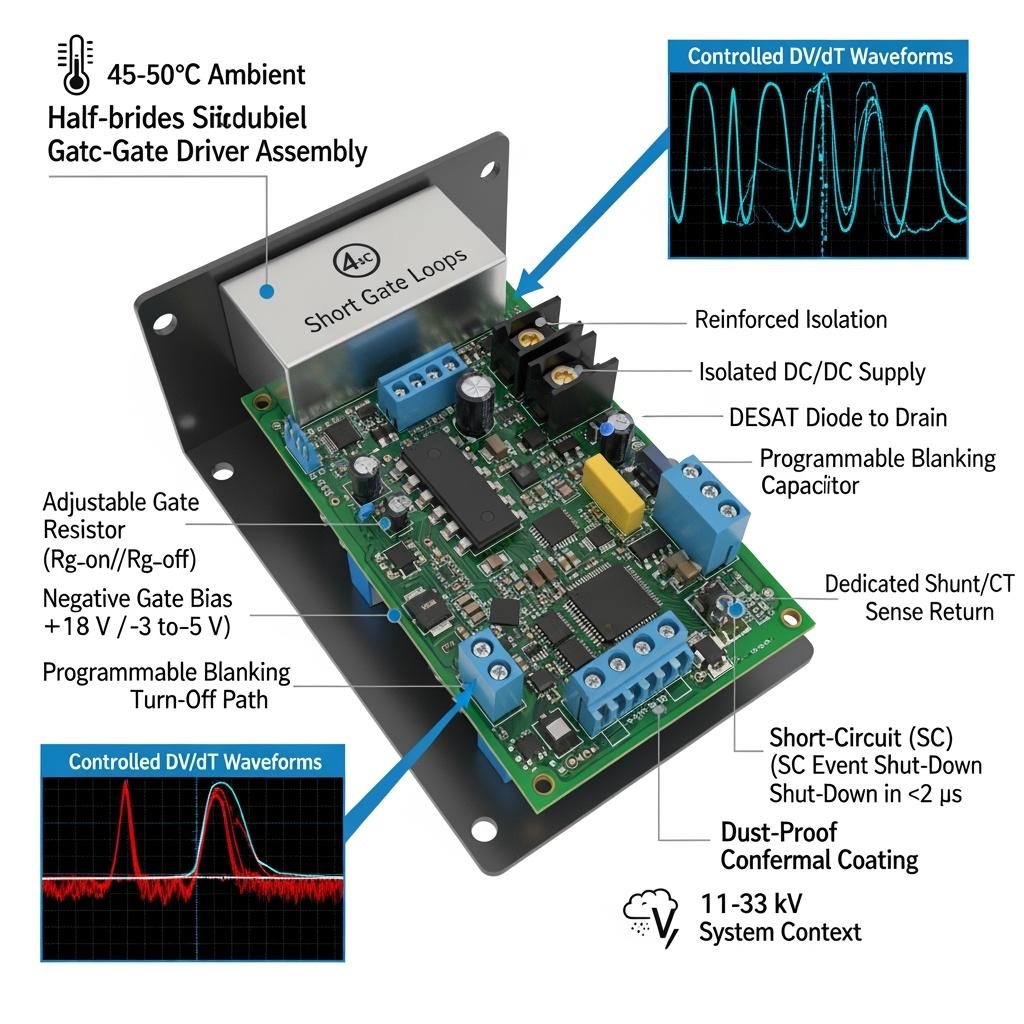

炭化ケイ素(SiC)MOSFETゲートドライバ回路は、高効率、高密度電力段の制御バックボーンです。スイッチング動作を決定し、dv/dtとdi/dtを管理し、短絡シャットダウンやDESATセンシングなどの重要な保護機能を提供します。パキスタンの繊維、セメント、 鉄鋼 電気室が45~50°Cの周囲温度と空中粉塵に直面しているセクターでは、堅牢なゲートドライバは、11~33 kV配電レベルの太陽光発電相互接続および産業用ドライブで、98.5%以上のインバータ効率、最大2倍の電力密度、長い動作寿命を達成するために不可欠です。

2025年、市場リーダーは、高速ミラープラトー遷移、短絡イベント中の狭い安全動作領域、高dv/dtエッジからのEMIに対する感受性など、SiCデバイスの物理学にゲートドライバ設計を合わせています。アプリケーション最適化ドライバは、高CMTI(>100 V/ns)、正確なターンオン/オフゲート抵抗、2レベルターンオフ(TLO)、耐性のための負のゲートバイアス、低遅延DESAT検出を組み合わせています。絶縁電源、強化デジタル絶縁、PCBレイアウトルール(ケルビンソース、低インダクタンスループ)と組み合わせることで、これらのドライバは損失を低減し、EMIを軽減し、モジュールを保護します。パキスタンの産業環境で一般的な粉塵、熱、グリッドの乱れの下でも。

技術仕様と高度な機能

- ドライブと絶縁

- ゲート電圧:+15~+20 Vターンオン、-3~-5 Vターンオフ(設定可能)

- ピークソース/シンク電流:大型SiCモジュールを駆動するための6~30 Aクラス

- 絶縁定格:システムMVコンプライアンスのための強化絶縁、CMTI ≥ 100 V/ns

- 絶縁DC/DC:低コモンモード容量

- スイッチング制御

- dv/dt管理:独立したRg_on/Rg_off、オプションの分割ゲートドライブ、アクティブMillerクランプ

- 2段階ターンオフ(TLO):障害発生時のVDSオーバーシュートを制限するソフトターンオフパス

- スルーレートシェーピング:損失とEMIのバランスを取るゲート電流シェーピングネットワーク

- 保護と診断

- DESATセンシング:プログラム可能なブランキング時間とソフトシャットダウンによる高速短絡検出;<2 µsの反応が一般的

- 過熱入力、シャントまたはRogowski/CTによる過電流、および障害バス信号による障害ラッチ

- ゲートモニタリング:オープンワイヤ検出、ゲートソース短絡検出、および決定論的障害処理を備えたUVLO

- 通信と制御

- インターフェース:デッドタイムエンフォースメント付きPWM;テレメトリ(障害、温度、イベントカウント)用のオプションのSPI/UART

- 安全のための冗長ディスエーブルライン;ウォッチドッグ/リセット統合

- 環境と信頼性

- コンフォーマルコーティングオプション、耐食性仕上げ、および拡張温度動作

- 機械的:低インダクタンスゲートループフットプリント、ケルビンソース接続、および現場サービス用の堅牢なコネクタ

説明的比較:SiC最適化ゲートドライバ対従来のIGBT/シリコンドライバ

| 基準 | dv/dt制御とDESATを備えたSiC最適化ゲートドライバ | 従来のIGBT/シリコンゲートドライバ |

|---|---|---|

| スイッチング周波数サポート | 正確なdv/dtシェーピングで50~150 kHz | 5~20 kHzが一般的;dv/dt制御が制限されている |

| CMTIとEMIの堅牢性 | Millerクランプと負バイアスで≥100 V/ns | 低いCMTI;誤ターンオンに対する感受性が高い |

| 短絡保護 | <2 µsの反応とソフトシャットダウンを備えたDESAT | 検出が遅い;障害時のストレスが高い |

| 効率への影響 | 低いスイッチング損失、高い周囲温度での安定動作 | 損失が高い;温度でのディレーティングが大きい |

| SiCモジュールとの統合 | ケルビンソース、分割ゲート抵抗器、高速保護 | SiC固有のレイアウトとタイミングが不足していることが多い |

専門家による引用による主な利点と実証済みのメリット

- 効率と密度:dv/dt制御と高いCMTIにより、より高いスイッチング周波数(50~150 kHz)が可能になり、パッシブサイズを削減し、コンパクトなフィルタと冷却で≥98.5%の効率をサポートします。

- 堅牢な保護:DESATとTLOにより、短絡またはシュートスルーイベントによる壊滅的な障害を防止し、ダウンタイムと保証リスクを削減します。

- EMI耐性動作:負のゲートバイアスとMillerクランプにより、誤ターンオンを抑制し、長いケーブルハーネスを備えたほこりの多い高温の電気室での安定性を維持します。

- より速い市場投入までの時間:事前検証済みのレイアウト、パラメータライブラリ、および診断テレメトリにより、11~33 kV PVおよび産業用ドライブの統合作業を削減します。

専門家の視点

「ワイドバンドギャップデバイスの利点を実現するには、ゲートドライバの設計が不可欠です。高いCMTI絶縁、制御されたdv/dt、および高速短絡保護は、信頼性の高いSiCパワーステージに不可欠です。」— IEEE Power Electronics Societyアプリケーションガイダンス(ieee.org)

実際のアプリケーションと測定可能な成功事例

- 配電レベルのPVインバータ(パキスタン南部):DESATとTLOを備えたSiCドライバは、故障に関連するモジュール損傷を削減し、dv/dtシェーピングはTHDマージンと≥98.5%の効率をもたらしました。安定した接合温度により、システムは冷却体積を約40%削減しました。

- 繊維工場のVFD:負バイアスと分割ゲート抵抗器により、高速過渡現象中の誤ターンオンが排除され、45~50°Cの周囲条件下での迷惑トリップが減少し、織機の稼働率が向上しました。

- セメントおよび鉄鋼ドライブ:サブ2 µs DESATアクションにより短絡堅牢性が向上し、IGBT時代の保護遅延と関連する付随的な損傷が削減されました。メンテナンスコールは、夏季のピーク負荷時に著しく減少しました。

選択とメンテナンスの考慮事項

- デバイスペアリング

- ドライバ電流と電圧スイングをモジュールゲート電荷と希望のスイッチング速度に合わせます。ケルビンソースの可用性を確認します。

- 負バイアスレベルを検証して、イミュニティと酸化物ストレスの制限のバランスを取ります。

- 保護調整

- モジュールの特性と予想される浮遊インダクタンスごとにDESATしきい値とブランキング時間を設定します。

- TLO抵抗器のサイズ設定を実装して、エネルギー散逸を長引かせることなくVDSオーバーシュートを制限します。

- PCB/レイアウト

- ループインダクタンスを最小限に抑えます。電源とロジックのグランドを分離します。DESATおよびセンスラインには専用のリターンを使用します。

- DC/DCおよびアイソレータを高いdi/dtノードから離して配置します。MVシステムに適した沿面距離/クリアランスを適用します。

- 環境の強化

- ほこりのためのコンフォーマルコーティングを適用します。高温コンポーネントを指定します。45~50°Cの周囲温度での動作を確認します。

- 検証

- dv/dtを調整するためのダブルパルス試験を実施します。TSC反応を検証するための短絡試験を実施します。伝導/放射エミッションのEMCプリコンプライアンス。

業界の成功要因と顧客の声

- モジュールパッケージングおよびLCLフィルタチームとの共同設計により、dv/dtターゲットをEMIおよびTHDの目標に合わせ、再設計ループを削減します。

- 早期のミッションプロファイル検証により、過剰設計とコストを削減し、信頼性を維持します。

お客様の声:

「高速DESATと2段階ターンオフをSiCハーフブリッジに統合することで、まれな短絡イベントによるフィールド障害が排除されました。dv/dt調整により、効率を犠牲にすることなくEMIヘッドルームが向上しました。」— シンド州のC&I PVインテグレータのリードパワーエンジニア

将来のイノベーションと市場トレンド

- リアルタイムの電流および温度センシングに基づく適応dv/dt制御を備えたデジタルゲートドライバ

- ゲート電荷およびしきい値ドリフト追跡用の統合状態監視(SOHメトリック)

- マルチMW MVシステム用のより高いCMTI絶縁技術とより低いコモンモード容量

- パキスタンのMV PVパイプライン(>5 GW)向けに調整されたリファレンス設計と、ローカル製造サポート

よくある質問と専門家による回答

- SiC MOSFETで負のゲートバイアスを使用する理由

高いdv/dtでのMiller結合による誤ターンオンを防止するため。一般的な値は-3~-5 Vで、デバイスの制限とEMIの目標ごとに選択されます。 - DESAT保護はどのくらいの速さであるべきか

障害発生から電流遮断までの合計反応時間を約2 µs以内にし、過電圧ストレスを制限するためにソフトシャットダウンを行います。 - 2段階ターンオフとは何か、なぜそれを使用するのか

TLOは、障害時に制御された、よりソフトなターンオフを導入し、VDSオーバーシュートと浮遊インダクティブリンギングを低減し、モジュールとゲート酸化膜を保護します。 - 効率を損なうことなくdv/dtを調整するにはどうすればよいですか

分割Rg_on/Rg_off、インダクタンスを低減するためのレイアウト、およびオプションのゲート電流シェーピングを使用します。EMIとスイッチング損失のバランスを取るために、ダブルパルス試験を繰り返します。 - これらのドライバは、ほこりの多い45~50°Cで確実に動作しますか

はい。コンフォーマルコーティング、ディレーティングされたコンポーネント、適切なエアフローまたはシーリングにより、ドライバは安定性と保護性能を維持します。

このソリューションがお客様の業務に役立つ理由

これらのSiCに焦点を当てたゲートドライバ回路は、パキスタンのMV相互接続および高負荷産業用ドライブに必要な制御精度と保護速度を提供します。これにより、コンパクトなLCLフィルタのスイッチング周波数を高くし、高温でほこりの多い環境での動作を安定させ、損傷を伴う障害から保護し、≥98.5%の効率、最大2倍の電力密度、および繊維、セメント、鉄鋼アプリケーション全体での長い耐用年数を実現します。

カスタムソリューションについては専門家にご相談ください

専門家のドライバ設計と検証でSiCパワーステージを加速します。

- 10年以上のSiC製造専門知識とアプリケーションエンジニアリング

- 絶縁、保護、EMI制御におけるイノベーションを推進する主要な研究エコシステムのバックアップ

- 熱的および機械的信頼性に影響を与えるR-SiC、SSiC、RBSiC、およびSiSiCコンポーネント全体でのカスタム製品開発

- ローカルドライバアセンブリおよびテスト用の技術移転および工場設立サービス

- デバイスとドライバからフィルタ、冷却、コンプライアンスまでのターンキーソリューション

- 効率、信頼性、およびより速い市場投入までの時間を実現する19以上の企業による実績のある結果

無料相談と、調整されたゲートドライバ仕様パッケージをリクエストしてください。

- Eメール:[email protected]

- 電話/WhatsApp:+86 133 6536 0038

MV PVおよび産業用ドライブのロールアウトに合わせて、2025〜2026年の開発スロットを今すぐ予約して、共同設計、EMC検証、およびフィールドパイロットを確保してください。

記事のメタデータ

最終更新日:2025年9月10日

次回の予定更新日:2026年1月15日

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.