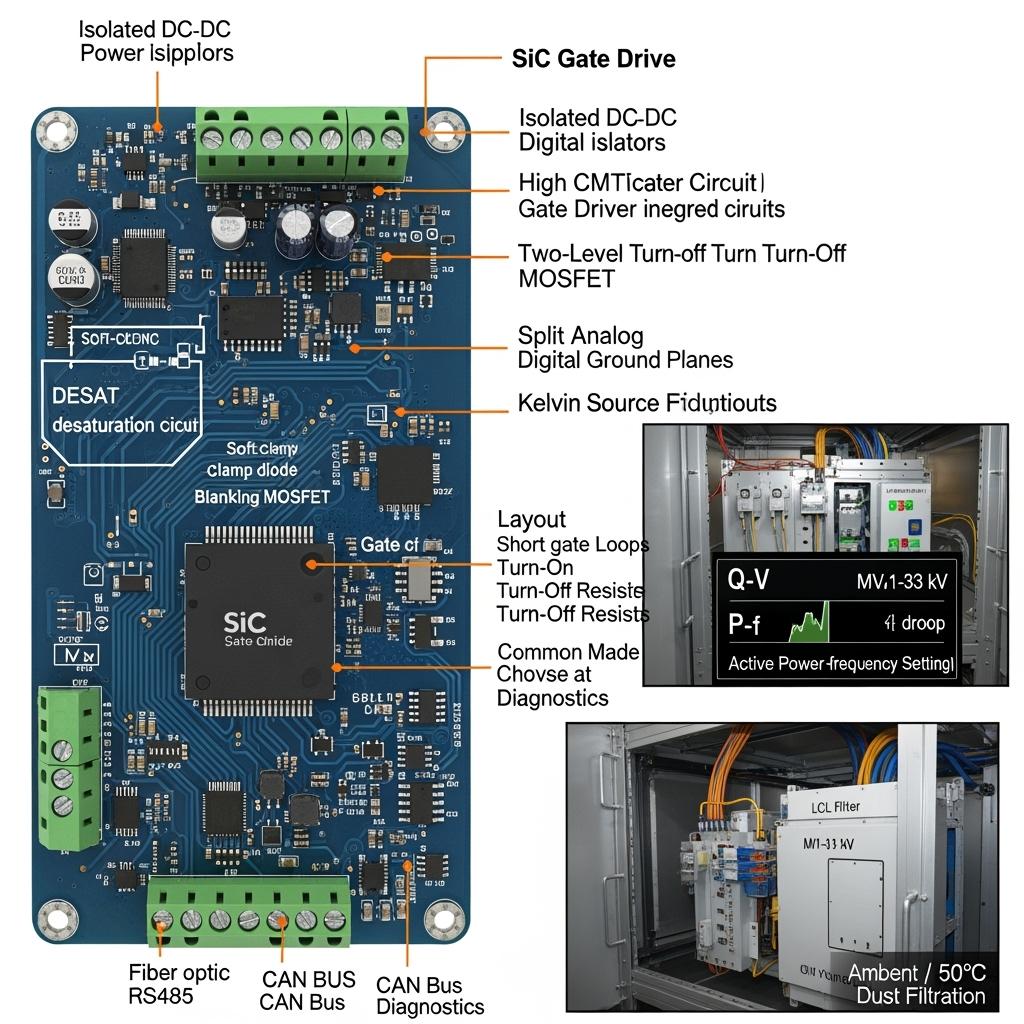

SiC Gate-Drive Solutions Tailored for Energy Storage Systems with DESAT Protection, dv/dt Control, and Grid-Support Coordination

Share

Product Overview and 2025 Market Relevance

SiC gate-drive solutions are the control and protection nerve-center for high-performance battery energy storage system (BESS) power conversion systems (PCS) and MV inverters. In Pakistan’s textile, cement, steel, and fast-growing data center segments, grid volatility on 11–33 kV feeders, high ambient temperatures (45–50°C), and dusty environments demand gate drivers that unlock SiC speed and efficiency without compromising reliability.

Modern SiC MOSFETs switch at 50–200 kHz with steep dv/dt. The gate drive must deliver precise gate charge control, robust isolation, and coordinated protection. Sicarb Tech’s tailored SiC gate-drive boards integrate:

- DESAT protection with two-level turn-off (TLO) to limit fault energy and prevent device overstress

- dv/dt shaping via adjustable gate resistors, active Miller clamp, and negative gate bias for clean turn-off

- High CMTI isolation for noisy environments

- Coordination with PCS control—PLL/grid-following and grid-forming modes, Q–V (Volt/VAR), P–f droops, and active LCL damping—to meet MV interconnection expectations while achieving ≥98% converter efficiency

For Pakistan’s 2025 outlook—3–5 GWh of new C&I and grid-side storage, tariff-driven peak shaving, and utility requirements for fault ride-through (FRT) and reactive support—SiC-aware gate-drive platforms are pivotal to accelerate commissioning, pass compliance, and sustain high uptime.

Technical Specifications and Advanced Features

- Electrical and isolation

- Gate voltage: +15 to +18 V turn-on; -3 to -5 V turn-off (configurable)

- Peak gate current: 8–30 A class drivers for fast edges with controlled EMI

- Isolation rating: reinforced isolation; CMTI ≥ 100 V/ns to tolerate fast dv/dt

- Propagation delay matching: ≤30–50 ns channel-to-channel for symmetric switching

- Protection

- DESAT detection with blanking (e.g., 200–800 ns) and soft-turn-off path (TLO) to curb overshoot and reduce fault energy

- UVLO/OVLO on gate bias rails; short-circuit withstand coordination (SCWT)

- Active Miller clamp to suppress parasitic turn-on under high dv/dt

- dv/dt control and EMI

- Independent turn-on/off Rg networks; optional RC snubbers for harsh layouts

- Kelvin source pin connection to minimize source inductance

- Programmable slew rate profiles for different grid modes or load states

- Control coordination

- Interfaces to main control boards implementing PLL, grid-following and grid-forming control, Q–V and P–f droops, active damping for LCL

- Event logs and timestamped fault capture for faster root-cause analysis

- Environmental and reliability

- Operating temperature: -40°C to +105°C ambient; conformal coating options

- HAST/THB-qualified components; surge and ESD protections for field robustness

- Diagnostics and security

- Real-time telemetry: gate voltage, fault flags, temperature

- Secure firmware updates; protected parameter sets for utility witness testing

Performance Comparison for Energy Storage PCS and MV Inverters

| Criterion | SiC-tailored gate-drive with DESAT, dv/dt control, and grid coordination | Generic gate-drive for silicon IGBTs |

|---|---|---|

| Switching frequency range | 50–200 kHz with clean waveforms | 5–20 kHz typical; limited at higher freq |

| Protection response | Fast DESAT + TLO minimizes fault energy | Slower OCP; higher device stress |

| EMI and THD impact | dv/dt shaping + Kelvin source lowers EMI; smaller LCL filters | Higher overshoot; larger filters |

| Grid support integration | Native Q–V, P–f, GFM/GFL coordination | External/limited; slower commissioning |

| Uptime in harsh sites | High CMTI, robust isolation, coated PCBs | Susceptible to noise and humidity |

Key Advantages and Proven Benefits with Expert Quote

- Efficiency and density: Clean high-frequency switching reduces filter size and losses, pushing PCS efficiency toward ≥98% with 1.8–2.2× power density.

- Reliability under faults: DESAT with two-level turn-off contains fault energy, reduces overshoot, and protects expensive SiC modules.

- Faster grid acceptance: Coordinated control features (FRT, Q–V, P–f) streamline MV interconnection compliance and reduce commissioning time.

Expert perspective:

“Gate drivers for wide bandgap devices must combine fast protection and precise slew control to realize efficiency gains without sacrificing reliability.” — IEEE Transactions on Power Electronics, WBG driver design guidance (https://ieeexplore.ieee.org)

Real-World Applications and Measurable Success Stories

- Punjab industrial park BESS (2 MW/4 MWh): SiC gate-drives with DESAT/TLO cut hard-switch fault energy by >40% vs legacy design and enabled ~100 kHz operation. PCS efficiency improved to 98.2%, cabinet volume reduced by 35%, and grid acceptance accelerated with pre-validated FRT settings.

- Textile VFDs in Sindh: dv/dt-controlled gates reduced EMI-induced trips and motor insulation stress. Plants reported improved uptime during 50°C summers and lower maintenance frequencies.

- MV inverter pilot in southern Pakistan: Grid-forming coordination stabilized voltage during feeder sags; reactive support (Q–V) maintained power quality, passing utility tests on first attempt.

Selection and Maintenance Considerations

- Device compatibility

- Match driver peak current and negative bias to target SiC modules; ensure Kelvin source is available.

- Layout and parasitics

- Keep gate loop area minimal; employ laminated busbars and split ground to reduce CM coupling.

- Protection tuning

- Set DESAT thresholds per module datasheet and mission profile; adjust blanking to avoid false trips while catching real faults.

- Thermal and environment

- Validate driver thermals and conformal coating for dust/humidity; plan filter maintenance intervals.

- Commissioning workflow

- Use parameter packs for Q–V, P–f, and LCL damping; conduct double-pulse testing before full-power trials.

Industry Success Factors and Customer Testimonials

- Cross-discipline co-design among gate-drive, module, magnetics, and control firmware is crucial for achieving high efficiency with low EMI.

- Remote diagnostics and event logging shorten root-cause analysis and improve fleet reliability.

Customer feedback:

“The SiC-specific driver platform eliminated our nuisance trips and let us push frequency higher without EMI penalties. Commissioning on a weak feeder was finally predictable.” — Head of Power Electronics, local ESS integrator

Future Innovations and Market Trends

- Integrated current sensing and junction temperature estimation in gate drivers to power predictive maintenance

- Adaptive slew-rate control responding to grid events (sags/swells) to maintain stability with minimal losses

- Enhanced cyber-secure update frameworks for critical infrastructure

- Localization of driver production and test in Pakistan to cut lead times and enable faster service

Common Questions and Expert Answers

- How does DESAT with two-level turn-off protect SiC modules?

It detects overcurrent within hundreds of nanoseconds and transitions to a controlled, slower turn-off path that limits voltage overshoot and device stress. - What CMTI rating is needed for SiC switching at 100 kHz?

Aim for CMTI ≥ 100 V/ns with reinforced isolation and careful PCB partitioning to tolerate fast edges and minimize false triggering. - Do I need negative gate bias?

Yes, typically -3 to -5 V to prevent parasitic turn-on from Miller capacitance at high dv/dt, especially in half-bridge configurations. - Can the driver help pass utility interconnection tests?

Drivers coordinated with main control (Q–V, P–f, FRT) and active damping provide stable operation that eases testing and reduces on-site tuning. - How should I set DESAT thresholds?

Base them on device SOA and expected peak currents; validate with double-pulse tests and staged load steps to balance protection speed and immunity.

Why This Solution Works for Your Operations

Pakistan’s industrial environments push PCS and inverter hardware to the edge: weak feeders, high ambient heat, and dust. SiC gate-drive solutions with DESAT protection, dv/dt control, and grid-support coordination translate SiC device potential into field-proven outcomes—≥98% efficiency, compact filters and cooling, fewer trips, and faster compliance. The result is higher uptime, lower opex, and a shorter path to positive ROI.

Connect with Specialists for Custom Solutions

Work with Sicarb Tech to de-risk your SiC programs end-to-end:

- 10+ years of SiC manufacturing and application engineering expertise

- Backing from the Chinese Academy of Sciences (Weifang) Innovation Park

- Custom product development across R-SiC, SSiC, RBSiC, and SiSiC, plus advanced gate-drive and control platforms

- Technology transfer and factory establishment services for localized production and test in Pakistan

- Turnkey delivery from materials and devices to drivers, modules, cooling, and compliance documentation

- Proven track record with 19+ enterprises delivering higher efficiency, faster commissioning, and reliable operation

Book a free consultation to define your gate-drive specs, protection thresholds, and commissioning plan:

- Email: [email protected]

- Phone/WhatsApp: +86 133 6536 0038

Secure 2025–2026 co-design and validation slots to accelerate grid code compliance, reduce EMI risk, and scale deployments across Pakistan’s industrial hubs.

Article Metadata

Last updated: 2025-09-10

Next scheduled update: 2026-01-15

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.