Silicon Carbide MOSFET Gate-Drive Control Boards with Active Miller Clamp, Negative Bias, and High-CMTI Isolation for 50–200 kHz Operation

Share

Product Overview and 2025 Market Relevance

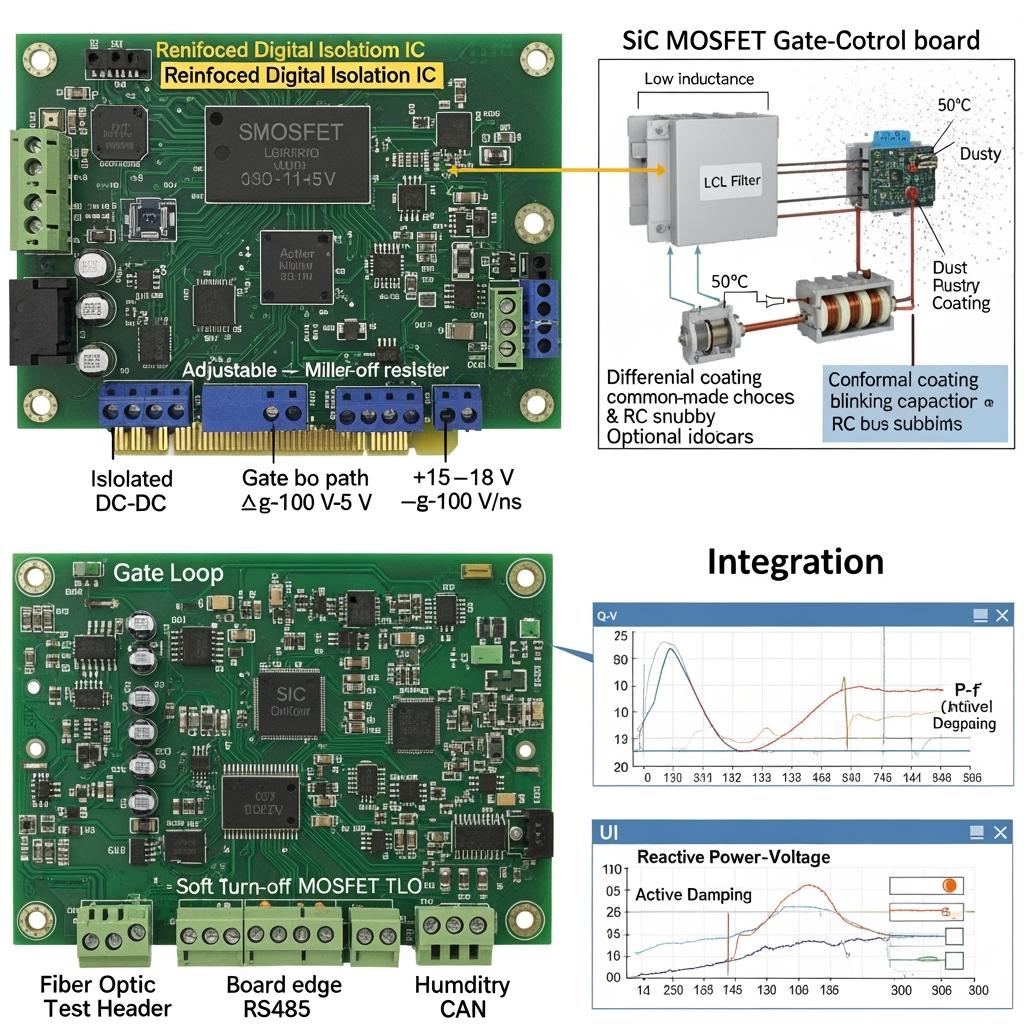

Silicon carbide (SiC) MOSFET gate-drive control boards are the keystone for unlocking high-frequency, high-efficiency operation in battery energy storage system (BESS) power conversion systems (PCS) and MV inverters. In Pakistan’s textile, cement, steel, and emerging industrial sectors, converters must deliver ≥98% efficiency, compact footprint, and stable operation on volatile 11–33 kV feeders—all while enduring 45–50°C ambient temperatures and dust-laden environments common in industrial parks.

Purpose-built SiC gate-drive boards enable precise, repeatable switching at 50–200 kHz by combining:

- High-CMTI reinforced isolation to tolerate fast dv/dt edges without false trips

- Active Miller clamp and configurable negative gate bias to suppress parasitic turn-on

- DESAT protection with two-level turn-off (TLO) for fast, controlled fault handling

- Tight propagation delay matching for symmetric half-bridge switching

- Interfaces that coordinate with PCS controls for LCL active damping, grid-following (GFL) and grid-forming (GFM) modes, Q–V and P–f droops, and FRT behavior

These features translate into measurable gains: smaller magnetics and filters, shorter commissioning on weak feeders, fewer nuisance trips, and improved uptime in harsh conditions. For 2025 deployments as Pakistan adds 3–5 GWh of C&I and grid-side storage, SiC-optimized gate-drive boards de-risk programs and accelerate ROI.

Technical Specifications and Advanced Features

- Electrical and isolation

- Gate voltage rails: +15 to +18 V turn-on, -3 to -5 V turn-off (configurable modules)

- Peak drive current: 8–30 A class for crisp edges with managed EMI

- Isolation strength: Reinforced insulation meeting relevant IEC/UL; CMTI ≥ 100 V/ns for 50–200 kHz switching

- Propagation delay and skew: ≤100 ns total propagation, ≤30–50 ns channel-to-channel skew

- Protection and fault handling

- DESAT protection with programmable blanking (e.g., 200–800 ns) and soft two-level turn-off to limit overvoltage

- UVLO/OVLO on both positive and negative rails; Miller clamp activation thresholds tuned to device Cgd

- Programmable fault latching, fault counters, and timestamped logs

- dv/dt control and EMI

- Independent turn-on/off Rg; optional split gate resistor footprints for fine tuning

- Kelvin source pin routing and star-ground topology to reduce inductive coupling

- Optional RC snubbers and dV/dt slew control profiles loaded via firmware

- Control coordination and interfaces

- Digital links to main control boards implementing PLL, GFL/GFM, Q–V, P–f droops, active LCL damping, and FRT curves

- Telemetry: gate voltages, DESAT events, temperature sensors; optional fiber isolation for noisy environments

- Environmental robustness

- Operating ambient: -40°C to +105°C; components rated for high humidity; conformal coating options

- ESD/surge protection on I/O; coating clearance maintained for creepage/clearance

Performance Comparison: SiC-Optimized Gate Drives vs Conventional IGBT-Oriented Drivers

| Criterion | SiC MOSFET gate-drive control boards (50–200 kHz optimized) | Conventional IGBT-oriented gate drivers |

|---|---|---|

| Switching frequency capability | 50–200 kHz with dv/dt control | 5–20 kHz typical; limited at higher fsw |

| dv/dt immunity (CMTI) | ≥100 V/ns reinforced isolation | Lower CMTI; higher false-trip risk |

| Fault protection | DESAT + TLO, fast and controlled | Slower OCP; higher overshoot/stress |

| EMI and THD impact | Clean edges, smaller LCL filters | Larger filters; increased EMI |

| Commissioning on weak grids | Coordinated active damping & grid modes | Longer tuning; instability risk |

Key Advantages and Proven Benefits with Expert Quote

- Higher efficiency and density: Stable high-frequency switching supports compact LCL filters and magnetics, enabling ≥98% PCS efficiency and >30% volume reduction.

- Robust protection and uptime: DESAT with controlled TLO limits fault energy and overshoot, protecting costly SiC modules and minimizing trips.

- Faster interconnection compliance: Built-in coordination with droop controls, FRT, and active damping accelerates MV grid acceptance.

Expert perspective:

“Gate drivers for wide bandgap transistors must provide fast, deterministic protection and finely controlled slew rates to realize efficiency advantages without compromising reliability.” — IEEE Transactions on Power Electronics, WBG gate-driver design guidance (https://ieeexplore.ieee.org)

Real-World Applications and Measurable Success Stories

- Punjab 2 MW/4 MWh PCS: SiC drivers with DESAT/TLO and active damping presets enabled ~100 kHz operation, lifted system efficiency to 98.2%, cut cabinet volume by 35%, and shortened commissioning by ~30% despite weak feeder conditions.

- Textile plant drives in Sindh: Negative bias and Miller clamp eliminated parasitic turn-on, reducing EMI trips during 50°C summers. Uptime improved and maintenance intervals were extended.

- MV inverter pilot in southern Pakistan: GFM coordination stabilized voltage during sags; reactive support (Q–V) met power quality targets, achieving first-pass utility approval.

Selection and Maintenance Considerations

- Device compatibility and sizing

- Match driver peak current to module gate charge (Qg) and desired dv/dt; ensure Kelvin source pins are available.

- PCB layout and parasitics

- Keep gate loop area minimal; use tight coupling to return paths and segregate high dv/dt nodes from logic traces.

- Protection tuning

- Set DESAT thresholds from datasheet SOA; calibrate blanking to avoid noise triggers while capturing real faults; verify two-level turn-off timing.

- Environmental hardening

- Apply conformal coating and select corrosion-resistant finishes; plan dust filter maintenance for cooled enclosures.

- Validation workflow

- Run double-pulse tests to tune Rg and slew; correlate DESAT/TLO behavior; HIL test active damping and droop interactions prior to full-power trials.

Industry Success Factors and Customer Testimonials

- Cross-team co-design linking gate-drive, power layout, LCL filter, and control firmware is pivotal for high-frequency stability and low THD.

- Parameter packs tailored to Pakistan utilities and feeder strengths accelerate field rollouts.

Customer feedback:

“The SiC-specific gate drivers removed our nuisance trips and let us increase switching frequency without EMI penalties. Grid tests were straightforward.” — Lead Power Engineer, Pakistan ESS integrator

Future Innovations and Market Trends

- Embedded junction temperature estimation and current sensing within gate drivers for predictive maintenance

- Adaptive slew-rate modulation responding to grid events to balance losses and stability

- Secure over-the-air updates with signed parameter packs for utility-witnessed tests

- Localization of driver assembly and test in Pakistan to reduce lead times and enhance service

Common Questions and Expert Answers

- Do I need negative gate bias for SiC MOSFETs?

Yes, typically -3 to -5 V helps prevent parasitic turn-on via Miller capacitance during high dv/dt transitions, especially in half-bridge legs. - What CMTI rating should I target?

Aim for ≥100 V/ns CMTI with reinforced isolation to avoid false triggering at 50–200 kHz switching. - How does two-level turn-off reduce fault stress?

TLO inserts a controlled, slower turn-off path after DESAT detection, limiting VDS overshoot and di/dt to protect the device and module. - Can these drivers help with weak-grid commissioning?

Yes. Coordination with active damping and droop controls stabilizes current and voltage during sags/swells, easing utility approvals. - How to tune Rg values?

Use double-pulse tests to balance switching loss and EMI. Employ separate turn-on/off resistors and, if needed, split-gate paths for finer control.

Why This Solution Works for Your Operations

Pakistan’s industrial environments are hot, dusty, and grid-challenged. SiC MOSFET gate-drive control boards with active Miller clamp, negative bias, high-CMTI isolation, and DESAT/TLO protection convert SiC’s device advantages into field results: ≥98% efficiency, compact footprint, fewer trips, and rapid grid compliance. The result is higher uptime, lower LCOE, and faster payback across textile, cement, steel, and emerging sectors.

Connect with Specialists for Custom Solutions

Partner with Sicarb Tech to design, validate, and scale SiC gate-drive platforms:

- 10+ years of SiC manufacturing and application engineering expertise

- Backed by the Chinese Academy of Sciences for device, packaging, and control innovation

- Custom development across R-SiC, SSiC, RBSiC, SiSiC materials and advanced gate-drive/control stacks

- Technology transfer and factory establishment services to localize production and test in Pakistan

- Turnkey solutions from materials and devices to gate drives, modules, LCL filters, cooling, and compliance documentation

- Proven track record with 19+ enterprises achieving higher efficiency, faster commissioning, and reliable operation

Request a free consultation for driver specification, protection tuning, and commissioning parameter packs:

- Email: [email protected]

- Phone/WhatsApp: +86 133 6536 0038

Secure 2025–2026 co-design and validation slots to accelerate grid code compliance, reduce EMI risk, and scale deployments across Pakistan’s industrial hubs.

Article Metadata

Last updated: 2025-09-10

Next scheduled update: 2026-01-15

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.