Obleas epiteliales de carburo de silicio de gran diámetro con perfiles de dopaje personalizados para la fabricación de dispositivos de 1200 V–3300 V y baja densidad de defectos

Compartir

Visión general del producto y relevancia para el mercado en 2025

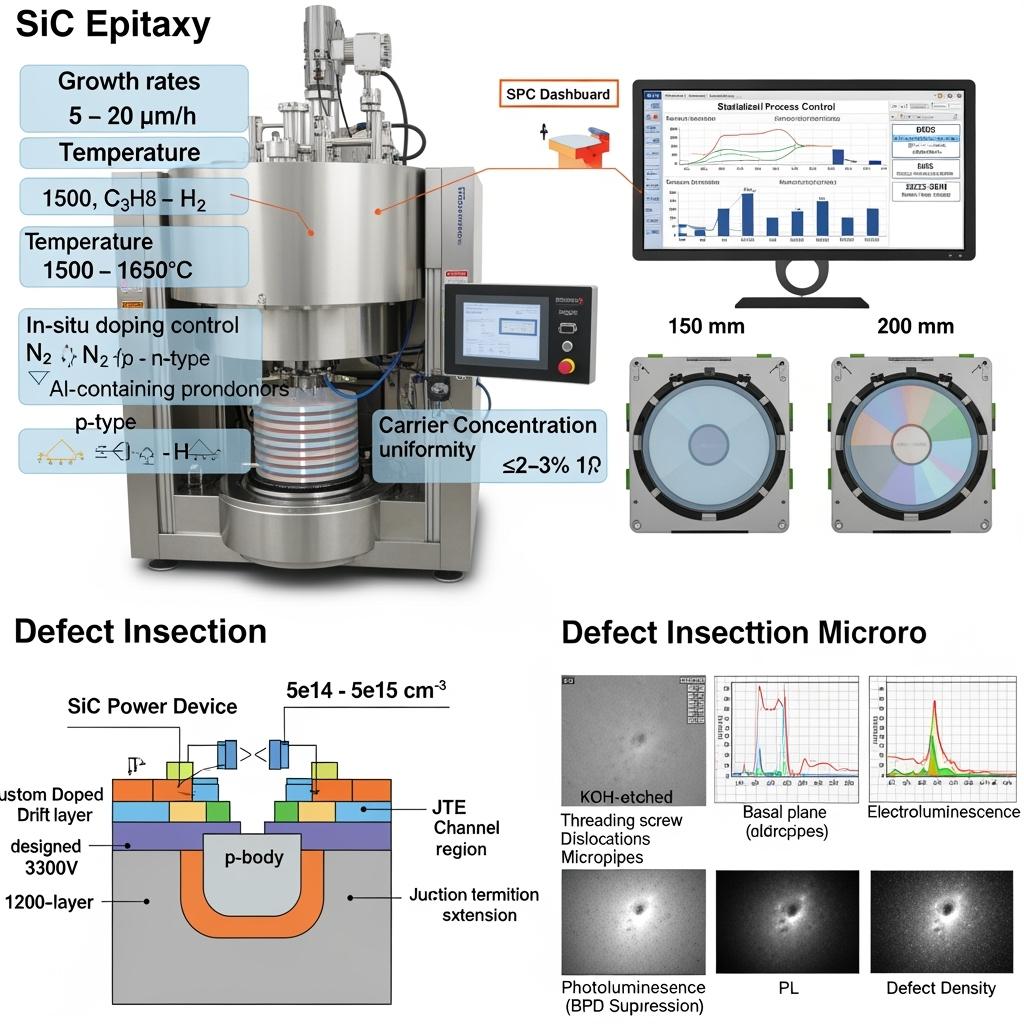

Las obleas epitaxiales de carburo de silicio (SiC) de gran diámetro, diseñadas con perfiles de dopaje personalizados y sustratos de baja densidad de defectos, son la base para dispositivos de alto rendimiento de 1200 V–3300 V utilizados en sistemas de conversión de energía (PCS) de sistemas de almacenamiento de energía de batería (BESS), inversores MV y accionamientos industriales. Para los sectores textil, cementero de Pakistán, siderúrgico, y los sectores industriales emergentes, donde la volatilidad de la red en los alimentadores de 11–33 kV, las altas temperaturas ambiente (45–50 °C) y el polvo son comunes, la calidad del dispositivo comienza en la capa epi. El control preciso del grosor y el dopaje de la epi, combinado con una defectuosidad ultrabaja, se traducen directamente en menores pérdidas de conducción y conmutación, mayor consistencia del voltaje de ruptura y mejor rendimiento, lo que en última instancia permite una eficiencia de PCS ≥98 % y una densidad de potencia de 1,8–2,2×.

Impulsores de 2025 para Pakistán:

- El rápido crecimiento en el almacenamiento C&I y del lado de la red (3–5 GWh en cinco años) exige dispositivos SiC confiables y de alta eficiencia para cumplir con los requisitos del código de la red (FRT, potencia reactiva, bajo THD).

- Las prioridades de localización favorecen a los socios que pueden adaptar las recetas de epi, proporcionar documentación del proceso y apoyar la transferencia de tecnología para acortar los plazos de entrega y aumentar el valor añadido nacional.

- Las duras condiciones ambientales requieren dispositivos con un comportamiento de fuga robusto, voltajes umbral estables y terminaciones de borde confiables, todo lo cual está influenciado por la calidad y uniformidad de la epi.

Sicarb Tech suministra obleas de gran diámetro (150 mm convencionales; hoja de ruta de 200 mm) con pilas epi personalizadas para MOSFET, diodos Schottky y diodos JBS, incluidas capas de deriva diseñadas, capas de cuerpo y extensiones de terminación de unión (JTE), todas calificadas para la fabricación de dispositivos de 1200 V, 1700 V, 2200 V y 3300 V.

Especificaciones técnicas y funciones avanzadas

- Diámetro de la oblea y sustrato

- 150 mm estándar; compatibilidad con la hoja de ruta de 200 mm

- Sustratos de micropipos bajos; procesos de supresión de tornillos de rosca (TSD) y dislocación del plano basal (BPD)

- Capas epitaxiales

- Grosor de la capa de deriva: 5–100 µm (rangos típicos por clase de voltaje), con uniformidad ±2–3 % en toda la oblea

- Concentración de dopaje: 5e14–5e16 cm^-3 (perfiles personalizados), con una tolerancia objetivo de ±10 % o mejor

- Pilas multicapa: capas epi JTE, ingeniería de canales y superficies listas para epi para la integridad del óxido de la puerta

- Calidad del dopaje y la interfaz

- Dopaje de tipo n a través de nitrógeno; tipo p a través de precursores de aluminio con efectos de memoria controlados

- Baja densidad de trampas para una mejor movilidad del canal y un voltaje umbral (Vth) estable

- Morfología de la superficie: rugosidad RMS optimizada para el óxido de la puerta y los pasos de implantación

- Control de defectos y metrología

- Mapeo de espesor y portador en línea; verificación SIMS de perfiles

- Grabado KOH para la evaluación de BPD/TSD; PL/EL para la uniformidad de la epi y la localización de defectos

- Detección previa de fugas y averías a través de estructuras de prueba; muestreo estadístico

- Preparación para la integración del proceso

- Recetas ajustadas para MOSFET de 1200 V–3300 V, diodos JBS y diodos Schottky

- Paquetes de documentación para la alineación de implantación/recocido y el diseño JTE

- Manipulación en sala blanca: FOUP/SMIF; flujos de trabajo compatibles con ISO 5–7

Perspectiva comparativa: Epi personalizado de bajo defecto frente a Epi de productos básicos para dispositivos SiC de alto voltaje

| Criterio | Epi SiC personalizado de bajo defecto (150/200 mm, perfiles personalizados) | Epi de productos básicos (perfiles genéricos) |

|---|---|---|

| Consistencia de la tensión de ruptura | Distribución BV ajustada a través del control preciso de deriva/JTE | Mayor dispersión de BV; más clasificación y caída |

| Pérdidas de conducción/conmutación | Menor RDS(on) por área; fugas estables | Mayores pérdidas; mayor variabilidad de las fugas |

| Rendimiento y rendimiento de las pruebas | Mayor rendimiento de la matriz; menos fallas de terminación de borde | Menor rendimiento; ciclos de prueba y reelaboración más largos |

| Fiabilidad en entornos hostiles | Mejor estabilidad de las fugas y control de la deriva de Vth | Mayor riesgo de deriva; fallas en la vida útil temprana |

| Localización y plazo de entrega | Transferencia de recetas y opciones de soporte local | Personalización limitada; cadenas de suministro más largas |

Ventajas clave y beneficios probados con la cita de un experto

- Mejora del rendimiento a nivel de sistema: menores pérdidas de dispositivos y BV más ajustados permiten una eficiencia de PCS ≥98 % y una reducción del tamaño de los imanes/refrigeración, lo que mejora el volumen del gabinete en >30 %.

- Rendimiento y costo: la epi de bajo defecto reduce la caída de las pruebas, aumenta las matrices por oblea en las clases de voltaje requeridas y estabiliza los programas de producción.

- Fiabilidad en las condiciones de Pakistán: la calidad de la epi impacta directamente en la deriva de las fugas, la estabilidad de la interfaz del óxido de la puerta y la robustez de la JTE, vitales para entornos de 45–50 °C y polvorientos.

Perspectiva experta:

“High-voltage SiC device performance is highly sensitive to epitaxial layer quality—thickness and doping uniformity, low defect densities, and engineered terminations are crucial for yield and reliability.” — IEEE Transactions on Electron Devices, SiC epitaxy and high-voltage device design (https://ieeexplore.ieee.org)

Aplicaciones reales e historias de éxito mensurables

- Plataforma MOSFET de 1200 V para PCS de 100–250 kW: la capa de deriva personalizada (10–12 µm, ~1e16 cm^-3) con morfología de superficie optimizada redujo RDS(on) del dispositivo en ~8–10 %, lo que contribuyó a una ganancia de eficiencia de PCS de 0,5–0,7 % a una conmutación de ~100 kHz en el almacenamiento C&I de Punjab.

- Diodos JBS de 1700 V para PFC y rueda libre: la epi con baja densidad de BPD y capas JTE a medida redujo la fuga inversa a 150 °C en ~30–40 %, lo que permitió disipadores de calor más pequeños y mejoró el tiempo de actividad en las fábricas textiles de Sindh.

- Piloto de 3300 V para inversor MV: la epi multicapa con una gradación precisa de la concentración de portadores logró una mejora de >50 % en la precisión de la distribución de BV, lo que redujo la caída de las pruebas y aceleró la certificación del lado de la red en el sur de Pakistán.

Selección y mantenimiento

- Clase de voltaje y perfil de misión

- Alinee el grosor de la deriva y el dopaje con el BV objetivo (1200/1700/2200/3300 V) y los perfiles de misión térmica típicos de los ciclos de trabajo industriales paquistaníes.

- Objetivos de defectuosidad

- Especifique las densidades máximas aceptables de BPD/TSD; asegúrese de que los proveedores de sustratos y epi proporcionen métricas KOH/PL y trazabilidad del lote.

- Interfaz y acoplamiento de procesos

- Coordine la preparación de la superficie de la epi con el crecimiento del óxido de la puerta, la implantación y la activación a alta temperatura (hasta 1700–2000 °C) para preservar la calidad de la interfaz y la estabilidad de Vth.

- JTE y terminación de borde

- Use capas JTE asistidas por epi para ajustar el BV y reducir las fugas de borde; verifique a través de TCAD y estructuras de prueba antes de las ejecuciones completas de la oblea.

- Cadena de suministro y EHS

- Asegure la manipulación FOUP/SMIF, la logística estable y la integración MES; planifique los búferes de stock locales para manejar los plazos de los proyectos de servicios públicos.

Factores de éxito del sector y testimonios de clientes

- La co-optimización a través de la epitaxia, la implantación/recocido y el diseño de terminación produce el mejor rendimiento y fiabilidad del dispositivo.

- El SPC ajustado y la metrología en línea minimizan la variabilidad de lote a lote, estabilizando el empaquetado posterior y la validación del sistema.

Comentarios de los clientes:

“Los perfiles epi personalizados ajustaron nuestra distribución de averías y redujeron las fugas, lo que se tradujo en una mayor eficiencia de PCS y un cumplimiento más fluido de la red”. — Director de Ingeniería de Dispositivos, OEM de electrónica de potencia con sede en Pakistán

Futuras innovaciones y tendencias del mercado

- Transición de oblea SiC de 200 mm con mejor rendimiento del reactor y control de uniformidad

- Técnicas de dopaje avanzadas y monitoreo in situ para perfiles más nítidos y efectos de memoria reducidos

- Placas de campo habilitadas para epi y estructuras de terminación para ajustar aún más el BV en clases de alto voltaje

- Vías de localización: empresas conjuntas para establecer el acabado de epi, la prueba de obleas y el montaje de módulos en Pakistán

Preguntas frecuentes y respuestas de expertos

- ¿Qué grosor y dopaje de epi necesito para los MOSFET de 1700 V?

Las capas de deriva típicas son ~12–15 µm con dopaje alrededor de 1e16 cm^-3 bajo; los valores exactos dependen de la arquitectura del dispositivo y de las compensaciones RDS(on)/BV deseadas. - ¿Cómo afectan los defectos como BPD a mis dispositivos?

Los BPD pueden promover la deriva de voltaje directo en los diodos e impactar las fugas; la epi de bajo defecto mejora la fiabilidad y reduce la deriva paramétrica. - ¿Puede la epi personalizada ayudar a reducir el tamaño del filtro LCL?

Indirectamente, sí. Las menores pérdidas de dispositivos a frecuencias de conmutación más altas permiten imanes y filtros más pequeños, dependiendo del co-diseño de la puerta y el control. - ¿Cómo asegura la uniformidad del dopaje en obleas de 150/200 mm?

A través de la optimización del flujo del reactor, el diseño del susceptor y el monitoreo in situ, con mapeo posterior al crecimiento y SPC para mantener la uniformidad dentro de ±2–3 % (grosor) y un control estricto del portador. - ¿Son las capas epi compatibles con la activación a alta temperatura?

Sí. Las superficies epi y los perfiles de dopaje están diseñados para soportar recocidos de 1700–2000 °C con tapas y limpiezas adecuadas para mantener la integridad de la interfaz.

Por qué esta solución es adecuada para sus operaciones

Para los programas industriales de PCS e inversores MV de Pakistán, la excelencia del dispositivo comienza con la epitaxia. La epi SiC de gran diámetro y bajo defecto con dopaje personalizado permite:

- Menores pérdidas de conducción/conmutación para una eficiencia ≥98 %

- Distribuciones

- Funcionamiento estable a 45–50°C, en entornos polvorientos, que admite un MTBF prolongado y una reducción del mantenimiento.

Esta base reduce el riesgo de fabricación, embalaje y puesta en marcha del sistema, lo que acelera el retorno de la inversión y la preparación para el mercado.

Conecte con especialistas para soluciones personalizadas

Asóciese con Sicarb Tech para especificar y entregar epi que cumpla con su hoja de ruta de dispositivos:

- Más de 10 años de experiencia en fabricación de SiC en materiales, epi y dispositivos.

- Respaldo de la Academia de Ciencias de China para la innovación y la metrología continuas.

- Desarrollo personalizado en componentes R-SiC, SSiC, RBSiC, SiSiC y pilas epi avanzadas.

- Servicios de transferencia de tecnología y establecimiento de fábricas para la capacidad local en Pakistán.

- Soluciones llave en mano desde epitaxia e implantación/recocido hasta pruebas de dispositivos, embalaje de módulos y cumplimiento.

- Trayectoria probada con más de 19 empresas que logran una mayor eficiencia, rendimiento y tiempo de comercialización.

Solicite una consulta gratuita para las especificaciones de epi, los objetivos de defectuosidad y los planes de integración de procesos:

- Email: [email protected]

- Teléfono/WhatsApp: +86 133 6536 0038

Asegure la asignación de obleas para 2025–2026 y las ranuras de transferencia de recetas para escalar la producción de dispositivos SiC para la creciente demanda de PCS e inversores MV de Pakistán.

Metadatos del artículo

Última actualización: 2025-09-10

Próxima actualización programada: 2026-01-15

About the Author: Sicarb Tech

We provide clear and reliable insights into silicon carbide materials, component manufacturing, application technologies, and global market trends. Our content reflects industry expertise, practical experience, and a commitment to helping readers understand the evolving SiC landscape.